Comprehensive Overview of MIPS Processor Control Signals and Data Flow

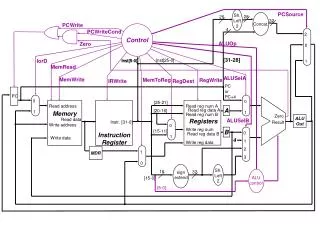

This document provides a detailed breakdown of the control signals and data paths involved in the operation of a MIPS processor. It outlines key processes including instruction fetching, execution, memory access, and write-back stages. The analysis covers various control signals such as MemRead, MemWrite, ALUSelA, ALUSelB, and others, illustrating how they interact during different operations like loading, storing, and executing R-type instructions. This serves as a foundational reference for understanding MIPS architecture and instruction processing.

Comprehensive Overview of MIPS Processor Control Signals and Data Flow

E N D

Presentation Transcript

Sh.Left2 2 0 1 Registers PC 0 0 Read reg num A Read address Read reg data A 1 1 Memory Read reg num B Zero Read data Instr. [31-0] Result Write address 0 Write reg num 0 Read reg data B InstructionRegister 1 Write data 1 Write reg data 2 1 ALUcontrol 3 0 Sh.Left2 signextend PCSource 28 26 Concat. 32 PCWrite Control 4 PCWriteCond ALUOp Zero Inst[25-0] [31-28] Inst[5-0] Inst[5-0] IorD MemRead ALUSelA MemWrite MemToReg RegWrite IRWrite RegDest PCorPC+4 [25-21] A [20-16] ALUOut ALUSelB [15-11] B 4 MDR 16 32 [15-0] [5-0]

MemRead=0MemWrite=0IRWrite=0ALUSelA=0 ALUSelB=3ALUOp=0PCWrite=0PCWriteCond=0RegWrite=0 Instr. Decode/Register Fetch IorD=0MemRead=1MemWrite=0IRWrite=1ALUSelA=0 ALUSelB=1ALUOp=0PCWrite=1PCSource=0RegWrite=0 Instr. Fetch LW or SW Jump MemRead=0MemWrite=0IRWrite=0ALUSelA=1 ALUSelB=2ALUOp=0PCWrite=0PCWriteCond=0RegWrite=0 BEQ Jump Branch Execution MemRead=0MemWrite=0 PCWrite=1RegWrite=0PCSource=2 Mem. Addr.Completion R-type MemRead=0MemWrite=0ALUSelA=1 ALUSelB=0PCSource=1ALUOp=1PCWrite=0PCWriteCond=1RegWrite=0 MemRead=0MemWrite=0IRWrite=0ALUSelA=1 ALUSelB=0ALUOp=2PCWrite=0PCWriteCond=0RegWrite=0 MemRead=1MemWrite=0IRWrite=0PCWrite=0PCWriteCond=0RegWrite=0 IorD=1 LW Memory Access SW MemRead=0MemWrite=1PCWrite=0PCWriteCond=0RegWrite=0 MemRead=0MemWrite=0RegDest=1PCWrite=0PCWriteCond=0RegWrite=1MemToReg=0 MemRead=0MemWrite=0 RegDest=0PCWrite=0PCWriteCond=0RegWrite=1MemToReg=1 Memory Access R-typeCompletion Write-back