Understanding Computer Architecture: Components and Their Functions

This presentation provides an overview of computer architecture, highlighting key components such as the processor, memory, and input/output systems. It explains how the CPU processes instructions, stores information, and handles data movement through buses. The fundamental binary encoding of information and the structure of memory are also discussed, alongside the roles of control units and arithmetic logic units (ALU). A focus on the instruction cycle and interaction protocols illustrates how these components cooperate to perform computing tasks efficiently.

Understanding Computer Architecture: Components and Their Functions

E N D

Presentation Transcript

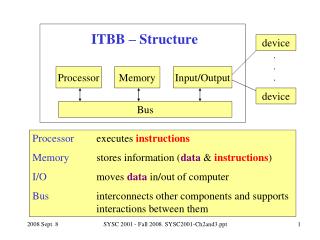

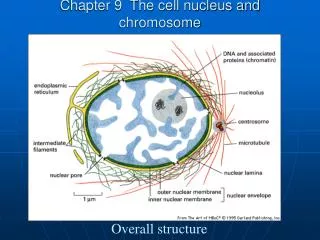

device . . . Processor Memory Input/Output ITBB – Structure device Bus Processor executes instructions Memory stores information (data & instructions) I/O moves data in/out of computer Bus interconnects other components and supports interactions between them SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

ITBB: Fundamental Binary Assumption • all information is binary encoded • result of transistor technology • one bit = one binary digit value either 0 or 1 • one Byte = 8 bits grouped together b7b6b5b4b3b2b1b0 e.g. 100111012 vs. 1001110110 • one word = machine dependent number of bits • information includes dataand instructions! case! msb lsb indicates base of number SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Encoding (Representing) Data Using Binary Values • counting numbers see Assignment 1 • integers (format defacto standard) • floating point (IEEE standard) • characters (ASCII, Unicode) • boolean • days of the week • colours • other ??? later – Ch. 9 later – assembly language application / implementation dependent ( SYSC 2003 ) SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Encoding (Representing) Instructions Using Binary Values • use some bits to encode operation opcode • use some bits to encode operands (if present) • for now, assume fixed number of bits ( w ) per instruction • fixed number of bits ( i ) used for opcode • fixed number of bits ( j ) used for operand(s) w bits opcode operands i bits j bits SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

ITBB Function Function lecture 2 • Recall functions in a computer: • Data PROCESSING • Data STORAGE • Data MOVEMENT • CONTROL • now we consider each component in terms of these functions and the roles of the components in the structure SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Processor ( a.k.a. CPU) CPU = Central Processing Unit • PROCESSINGarithmetic and logic unit ( ALU ) • manipulates/changes/combines/calculates data values • STORAGEregisters hold values in CPU • each register has a unique name • CONTROLcontrol unit • built-in instruction cycle engine that drives machine • instruction cycle drives control to memory and I/O components when appropriate ! SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Processor Structure • MOVEMENT • internal connections (control unit, ALU and registers) • external Bus connections to other components CPU ALU Registers Control Unit external Bus connections internal connections SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Processor Instruction Cycle START cycle fetch instruction ( from memory ) execute the instruction may cause more memory accesses (for operands) HALT SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

IMPORTANT SLIDE ! Memory ( 1 ) • STORAGE • fixed width locations (or cells) • each location contains information • contents: the value stored in the location • address: unique “name” for each location • MOVEMENT • internal connections • external bus connections e.g. house numbers memory does not differentiate contents as instructions vs. data ( its all just binary values ) SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Memory ( 2 ) • PROCESSING (limited processing compared to CPU) • refresh? transistor technology • bit-level error checking? error correction ? • CONTROL (of memory actions) • write – copy input value as new contents of a location • read – output (but do not modify) contents of a location • write / read driven from “outside” (e.g. processor, other ?) • may provide external control error condition? Ch. 5 later SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Memory Structure Memory memory processor locations Control Unit external Bus connections internal connections SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Input Output ( 1 ) • function depends on connected devices • STORAGE fixed width registers (or ports) • each register contains information • contents: the value stored in the register • address: unique “name” for each register • MOVEMENT • internal connections • external bus connections SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Input Output ( 2 ) Ch. 7 • PROCESSING • device dependent ! specialized hardware • CONTROL (of device-related processing) • write – copy input value as new contents of a port • read – output contents of a port • not always the case that can read & write a port ! • write / read driven from “outside” (e.g. processor, other) • may drive external control interrupts ! SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Input Output Structure N. B. I/O component = Memory ! device I/O device processor registers ( ports ) Control Unit external Bus connections internal connections SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Bus • pathway for interactions among components • standard signaling protocols for using the Bus • specified using timing diagrams • MOVEMENTYES! • CONTROL arbitration (traffic cop) • resolve concurrent requests to use the Bus • STORAGE not usually • PROCESSING not usually Appendix 3A sometimes … arbiter SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Interrupts • Mechanism to interrupt normal sequence of processing • Why? • I/O events: e.g. mouse click, network data arrives • timer: e.g. animation • program exception: e.g. overflow, division by zero • hardware error: e.g. memory error • these are asynchronous events! require programmed service • events caused by hardware, not software instructions Ch. 7.4 Unpredictable timing SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

interrupt handler (a.k.a. ISR) “driver”? An Interrupt Scenario independent execution contexts “threads of control” App. code eg. audio CD Suppose App. code executing: • interrupt occurs • want ISR to run • then resume App. ISR = Interrupt Service Routine performs s/w action appropriate to interrupt event eg. editor want to share processor between threads! SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

interrupt handler Transfer of Control via Interrupts App. code 5 2 interrupt occurs during execution of instruction at i 1 3 suspend thread ! hardware invokes interrupt handler resume thread @ i+1 6 4 SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Extending Instruction Cycle for Interrupts • after instruction execute phase of cycle – processor checks: • exception occurred? e.g. divide by 0 • interrupt event signal input to processor? • If interrupt pending: • Suspend and save context of current thread of execution • Set PC to start address of ISR • Continue Cycle fetch 1st instruction of ISR code • Eventually, ISR s/w restores context resume interrupted thread • If no interrupt pending: Continue Cycle fetch next instruction done by processor h/w – no s/w ! SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

hmmmm….. last 3 slides all say the same thing Extending Processor Instruction Cycle START cycle no interrupt pending save context & set PC to start address of interrupt handler fetch instruction execute instruction yes HALT SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Signals: “here is the data”, “read the contents of this address”, “I want to use the bus”, etc. Digital Signaling • signals are indicated as voltage levels • use particular levels to represent binary values • e.g. +5 volts 1 0 volts 0 • change values “quickly” Or could be –5V, 0V or…? want to avoid reading when not stable signals stable 1 0 time SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

App. 3A Signals and Timing Diagrams rising (leading) edge falling (trailing) edge ~ ~ • often bundle groups of related signals as one in a timing diagram e.g. 16-bit addresses 16 address signals one per bit 1 0 indefinite time elapsed signals stable, represent a useful 16-bit address signals may be stable, but do not represent a useful value 1 address 0 SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Bus • communication pathway connecting components • shared communications broadcast to all on bus • organize communicated information into 3 groups: • address • data • control of information being communicated everything else SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Data Bus • carries data • remember that there is no difference between “data” and “instruction” at this level • data bus width is a key determinant of performance • 8, 16, 32, 64 bit SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Address bus • identify the source or destination of data • e.g. CPU needs to read an instruction (data) from a given location in memory • address bus width determines maximum memory capacity of system (address space) • e.g. 8080 has 16 bit address bus giving 64k address space 216 SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Some Common Control Signals • reset – force all components to reset • clock(s) to synchronize communication • destination indicator – usually memory or I/O • acknowledgment from component – info received • interrupts • arbitration “hand shake” SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Bus Protocols • signaling and sequencing to permit interactions between components • processor puts address value on bus, and “memory read” control indication • memory receives read signal, reads address, gets appropriate data, puts data on bus • processor waits, then reads data from bus • May be • Synchronous - synchronized by a clock – organize protocol by clock “ticks” Ti • Asynchronous – no pacing by a shared clock e.g. memory read SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt

Single Bus Problems • lots of devices on one bus leads to: • propagation delays • long data paths mean that co-ordination of bus use can adversely affect performance • if aggregate data transfer approaches bus capacity • most systems use multiple buses to overcome these problems evolution for performance! SYSC 2001 - Fall 2008. SYSC2001-Ch2and3.ppt