Chapter 8 數位電路

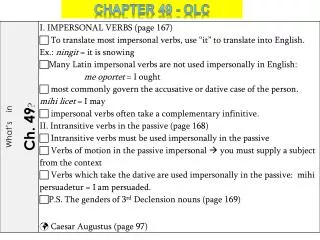

電子電路與實習. Chapter 8 數位電路. 四技一年級下學期 授課教師:任才俊. V i. V o. 數位反相器. 數位反相器的電路符號. 假設 V H 代表數位電路的高電位,而 V L 代表低電位,則反相器的功能是將輸入信號反相: 當 V i = V H , V o = V L 。 當 V i = V L , V o = V H 。. V o. slope = 1. V OH. slope = 1. V OL. V i. V OL V IL V IH V OH.

Chapter 8 數位電路

E N D

Presentation Transcript

電子電路與實習 Chapter 8數位電路 四技一年級下學期 授課教師:任才俊

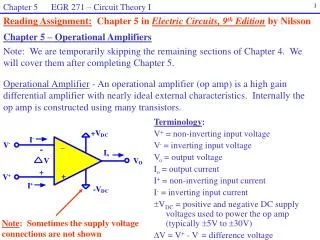

Vi Vo 數位反相器 • 數位反相器的電路符號 假設VH代表數位電路的高電位,而VL代表低電位,則反相器的功能是將輸入信號反相: 當Vi= VH,Vo= VL。 當Vi = VL,Vo= VH。

Vo slope = 1 VOH slope = 1 VOL Vi VOL VIL VIH VOH • 典型的反相器輸入電壓與輸出電壓的關係圖,稱為電壓轉換曲線(Voltage Transfer Curve, VTC) • VOL:正常低電位輸出電壓,對應輸入電壓Vi = VOH。 • VOH:正常高電位輸出電壓,對應輸入電壓Vi = VOL。 • VIL:可容許之最大低電位輸入電壓。 • VIH:可容許之最小高電位輸入電壓。

VIH及VIL定義為VTC中斜率等於 –1所對應的兩個輸入電壓 。 • 當 或 ,反相電路皆能正確將輸入電壓反相。 • 當 則進入模糊區間,此時反相電路無法將輸入電壓正確反相,是實際應用時必須避免發生的情況。

雜訊邊距 • 低電位雜訊邊距(low-level noise margin): • 高電位雜訊邊距(high-level noise margin): • 實用上NMH及NML愈大,表示電路愈不容易受雜訊影響,即電路愈穩定。

Vi VOH VOL t VOH (VOH+VOL)/2 VOL tPHL tPLH • 傳輸延遲 • tPHL(high-to-low propagation delay):輸入方波信號轉換電壓後,直到輸出信號由高電位(VOH)下降至 所需的時間。 • tPLH(low-to-high propagation delay):輸入方波信號轉換電壓後,直到輸出信號由低電位(VOL)上升至 所需的時間。

傳輸延遲 • 整體電路的傳輸延遲(tp)則取其平均值: • tp愈小代表元件的反應速度愈快,表示單位時間內能處理的資料量愈大。

功率損耗 • 靜態功率損耗(static power consumption):是指輸出端穩定地處於高電位或低電位時,電路所消耗的功率。 • 動態功率損耗(dynamic power consumption):是指輸出端在高低電位轉換期間,電路所消耗的功率。 • CMOS反相器的靜態功率損耗為零,是它的一大優點。

延遲-功率乘積(delay-power product): • 這個參數讓工程師能以客觀的方式,來比較不同電路在速度及功率兩方面合併考量下的優劣。因此以新的技術或設計降低 DP值才是工程師努力的方向。

VDD R Vo Vi 簡單FET反相器 • 由一顆N-channel FET加一電阻R所組成: • 當Vi = VDD(高電位)時,FET導通且工作在triode mode,等效上像一顆電阻(RON)。假如 • 當Vi = 0V(低電位)時,FET處於cutoff mode,

VDD R I Vo VDD Vi C R Vo Vi 當Vi = VDD時,Vo0V,此時電路消耗的功率為:而當Vi= 0V時,ID = 0,電路不消耗功率,POFF = 0。故其平均消耗功率為: 另一方面當Vi由VDD轉變為0V,使得Vo由0V轉變為VDD時,由於輸出端存在寄生電容(C),VDD經由R向C充電,顯然R愈大充電時間愈長,即Vo由0V上升至VDD的時間愈長,造成轉換速度變慢。

從功率損耗上考量,我們希望R愈大愈好;從速度上考量,我們希望R愈小愈好;所以FET反相器在實用上卻面臨功率損耗和速度兩者無法兼顧的困境。

VDD Qp Vi Vo Qn 天才設計-CMOS反相器 • 由N-channel MOSFET及 P-channel MOSFET組合而成,兩者具有互補作用,故稱為Complementary MOS(CMOS)。 用一顆P-channel MOSFET取代簡單反相器中的R

CMOS反相器的工作原理: • 當Vi = VDD時,Qn導通Qp不導通,Qn等效上像一顆電阻RON,但由於Qp不導通,所以: • 當Vi = 0V時,Qp導通Qn不導通,QP導通時等效上像一顆電阻RON,但由於Qn不導通,所以:

當Vi = VDD時,Qn導通但Qp不導通,故電源不需提供任何電流,即功率損耗為零。 • 當Vi = 0V時,Qp導通且Qn不導通,VDD經由Qp向輸出端寄生電容C充電。由於Qp的 RON很小,故充電速度很快。 • 所以CMOS在功率損耗和速度兩方面都很理想。

Vo slope = 1 VOH = VDD slope = 1 VOL = 0 Vi VIL VIH VDD CMOS反相器特性 • 電壓轉換曲線 • 假設使用enhancement-type的MOSFET,Vtn及Vtp分別表示Qn及Qp的臨界電壓(Vtn為正值,Vtp為負值)且Vtn = |Vtp| = Vt。 • Qn:VGS= ViVDS= VoVGS,eff= Vi Vt • QP: VSG = VDDViVSD= VDDVoVSG,eff= VDDVi Vt

電壓轉換曲線 • 理論上我們可以算出在VTC上斜率為 1所對應的兩個輸入電壓,即VIL及VIH;而正常的輸出高低準位分別為VOL及VOH:

雜訊邊距: • CMOS反相器在高低電位有相同的雜訊邊距

靜態功率損耗: • 當Vi= 0V,Vo= VDD,沒有電流由power supply流出,所以P = 0。 • 當Vi = VDD,Vo = 0V,由於Qp不導通,同樣沒有電流由power supply流出,故P = 0。 • 所以不管輸出電壓在高電位或低電位,整個電路不消耗任何功率,因此靜態功率損耗為零。

VDD Qp Vi Vo C Qn • 動態功率損耗 : • 當Vi由VDD變為0V時,Qp導通而Qn不導通,所以電源經由Qp向電容C充電,直到Vo= VDD為止。此時儲存在C上的電荷量為: • 每一次轉換期間(Vo由VLVHVL ),則皆由電源流出q = CVDD的電荷。假如反相器每秒鐘平均轉換次數為f,則轉換平均週期為:

平均在T時間內有q = CVDD的電荷由電源流出,故電源的平均電流為: • 所以平均功率損耗為: • 單位時間內轉換次數愈頻繁,則CMOS反相器所消耗的功率愈高。

VDD Qp Vi Vo C Qn • 傳輸延遲: CMOS反相器的傳輸延遲和輸出端的等效電容C有關,而C的大小和外接邏輯閘的個數有關。假設CMOS反相器外接n個邏輯閘並且每個邏輯閘的輸入端寄生電容皆相同,則C可以表示為: Cout:反相器本身輸出端的寄生電容量Cin:每個外接邏輯閘輸入端的寄生電容量 C = Cout+ n Cin

傳輸延遲(tp ): • tp= 0.5(tPLH tPHL) = • tp與VDD成反比而與C成正比,即VDD愈高充電速度愈快,C愈大充電速度愈慢。但是VDD愈高則功率損耗愈大,所以功率與速度之間必須適當取捨。 • 其中Vtn =

延遲-功率乘積(DP): • DP和C2成正比,並隨f及VDD上升而增加。由於數位電路的工作頻率f愈來愈高,欲降低DP值必須降低VDD,所以低電壓一直是IC設計努力的方向。

一個數位邏輯閘的輸出端所外接邏輯閘的個數稱為扇出數(fan- out)。 • 以BJT邏輯閘為例,外接邏輯閘會影響輸出電壓,若外接邏輯閘個數太多的話,會造成邏輯功能不正確,所以通常存在一個最大的扇出數(maximum fanout)。

CMOS邏輯閘的輸入端是絕緣體(IG= 0),所以外接邏輯閘不會影響輸出電壓,因此理論上CMOS邏輯閘的fanout可以趨近無限大 • 對於CMOS來說,當外接的邏輯閘數量增加時,輸出端的等效電容C隨之增加,結果tPHL及 tPLH也隨之上升,造成速度下降。 • 所以實用上隨不同的速度要求而定,CMOS邏輯閘的扇出數仍有所限制。

VDD A B Y B A CMOS邏輯電路 • CMOS反或閘(NOR gate) • 當A = VH或B = VH時,Y = VL。 • 當A = VL且B = VL時,Y = VH。 • 其邏輯功能為:

VDD B A Y A B • CMOS反及閘(NAND gate) • 當A = VH且B = VH時,Y = VL。 • 當A = VL或B = VL時,Y = VH。 • 其邏輯功能為:

VDD A B Y A B • 互斥或閘(XOR gate) • 當(A=VH,B=VL)或(A=VL,B=VH),Y=VH。 • 當(A=VL,B=VL)或(A=VH,B=VH),Y=VL。 • 其邏輯功能為: _ A _ B _ A _ B

B A S2 Y B A S1 傳輸閘邏輯電路 • 將FET 類比開關應用在數位邏輯上: • 當B = 1,S2閉合而S1打開,所以輸出 ,即Y的準位由輸入信號 所決定。 • 當B= 0,S1閉合而S2打開,所以輸出Y = A。 • 其邏輯功能為: _ _

B Y A B • 利用傳輸閘邏輯來完成XOR的功能: • S1及S2用類比開關來取代,結 果成為左圖的傳輸閘邏輯電路,結構顯然比之前用CMOS反相器的組合簡單。 • 邏輯功能為: _ A _ B

V1 V2 V3 反相器的應用 • 環型振盪器(ring oscillator) • 利用反相器存在傳輸延遲,使得Vo無法隨Vi瞬間改變的特性,我們可以串接奇數個(n 3)反相器成為一個環型振盪器,以產生穩定的方波信號。 • 如左圖,將三個反相器串接並將第三個反相器的輸出端接回第一個反相器的輸入端,形成一個迴路。這個迴路會自然產生方波信號。

假設迴路中有n個反相器(n為奇數且n 3),所得到方波信號的週期及頻率分別為: • 所以在tp固定的情況下,利用n可以控制頻率,故ring oscillator是IC中產生方波信號的簡便方法。

VCC RC Vo Vi Q BJT轉換特性 • 數位電路的應用上主要將BJT工作在cutoff及saturation兩個mode 由於PN-junction內部的電容效應,使得BJT無法瞬間由cutoff mode轉換至saturation mode,反之亦然。

n+ p n + VCE 電子流動方向 VBE + • 當Vi= VCC,BJT處於saturation mode 時,其Base充滿大量由Emitter而來的自由電子,此時Base類似一個儲存電荷的電容,當Vi瞬間由VCC降為0V時,原本累積在Base上的電荷並不會馬上消失,必須等待儲存電荷清除之後,BJT才會轉變至cutoff mode,使得Vo= VCC。這段時間稱為儲存時間(storage time, ts)。 • 當Vi由0V變成VCC時,由於B-E界面的電容效應,BJT無法瞬間由 cutoff mode轉換至saturation mode。必須等到B-E界面電容充電完成後,BJT才真正進入 saturation mode。這段時間延遲便是td。 一般而言ts >> td,所以如何降低ts 成為BJT數位電路設計上的重要考慮。

VCC RC Vo Vi Q 簡單BJT反相器 • 由一顆電晶體和一顆電阻所組成的電路 • 當Vi= VH = VCC,Q導通且工作於saturation mode, • 當Vi= VL = 0.2V,Q不導通,IC = 0, • 由於電阻RC的緣故,簡單BJT反相器面臨功率損耗和切換速度兩者無法兼顧的問題。

VCC RC Vo RB Vi Q • 在Vi = VCC的情況下,VCC直接跨在B-E界面,可能造成BJT因電流過大而燒燬,所以利用一顆額外的電阻RB隔離Vi及B極。使B極電壓VB約等於0.7V 。 左圖的BJT數位電路,主要由電阻和電晶體所組成,稱為Resistor-Transistor Logic (RTL)

Resistor-Transistor Logic (RTL) • 當Vi = VCC時: • 必須適當選擇RB和RC,才能使BJT工作在saturation mode。所以:

VCC = 5V R2 1.6K R4 130 R3 4K Q2 D Vi Q3 Vo Q4 Q1 R1 1K TTL邏輯電路 • TTL inverter的標準電路 • 當Vi= VH,各個電晶體的工作模式為:Q4:inverse active modeQ3:saturation modeQ1:saturation modeQ2:cutoff modeD:OFF • 當Vi= VL(假定VL= 0.2V),各電晶體工作模式為:Q4:saturation modeQ3:cutoff modeQ1:cutoff modeQ2:active modeD:ON VBE(ON) = 0.7VVCE(sat) = 0.2V

當Vi = VH,IIH14.5A是一個很小的電流,而IIH是由前級電路所提供。換句話說,Q4可以降低前級電路的輸出電流,因此增加前級電路的fanout (前級電路亦為TTL)。 • 當Vi= VH,VC4= 1.4V。當Vi由 VH轉變為VL的瞬間,由於寄生電容效應所以VC4暫時仍維持在1.4V,此時Q4處於active mode,造成大量電流流出Q3的B極,使Q3迅速由saturation mode轉為cutoff mode,有效降低storage time(ts)。

當Vi = VL,Vo= VH。當Vi由VL轉變為VH的瞬間,由於寄生電容效應使Vo仍暫時維持在高電位,此時Q1處於active mode。由於Q1的B極電流很大(2.64mA),造成很大的IC(IC= IB),可以很快將輸出端寄生電容累積的電荷放電,使Vo迅速由高電位降為低電位。 • 在正常情況下,Q2在active mode 與cutoff mode間作切換,所以沒有ts的問題,可以快速轉換。(這是採用此結構的重要因素)

Q2和Q1導通時分別將Vo提高及拉低,分別稱為pull-up transistor 及pull-down transistor。這種作法稱為active pull-up及active pull-down,乃是用主動元件(電晶體)來達成電位改變的設計方法,如此可以加速輸出電位的轉換。

Vo 3.7V 2.7V 0.1V Vi(V) 0.5 1.2 1.4 TTL特性 • 電壓轉換曲線 在輸出端不接任何邏輯閘的情況下: VOH 3.7V,VOL 0.1VVIH 1.4V,VIL 0.5VNML = VIL – VOL = 0.4VNMH = VOH – VIH = 2.3V

市售標準的TTL IC其規格為:(在輸出端外接十個邏輯閘的情況下): • 由此可以看出TTL的特性不及CMOS那麼好。 VOH = 2.4V,VOL = 0.4V VIH = 2V,VIL = 0.8VNML = VIL – VOL = 0.4VNMH = VOH – VIH = 0.4V

TTL族群: • 市面上常見的標準TTL積體電路有編號54 xx(54-系列)及編號74 xx(74-系列)兩個系列。 • 由於標準TTL的特性不是很好,所以許多類似的TTL電路陸續被設計出來,以得到更快的速度或更小的功率損耗。

VCC R1 R2 Vo S1 S2 Io ECL邏輯電路 • Emitter-Coupled Logic(ECL)設計主要源於一個很特別的「瓜分電流」的觀念。 • S1和S2 為開關。假設流經R1、R2的電流分別為I1和I2,則: • 若S1“close”,S2“open”,則: • 若S1“open”,S2“close”,則: I1 I2= Io I1 = Io,I2= 0Vo= VCC I2R2 = VCC (高電位) I1 = 0 ,I2= IoVo= VCCIoR2(低電位)

I1Io,I2 0Vo VCC(VH) VCC R1 R2 I1 0,I2 IoVo= VCCIoR2(VL) Vo V1 V2 Q2 Q1 Io • 用兩顆BJT來取代兩個開關S1&S2: • 由於Q1和Q2的射極接在一起,且在active mode時IC對VBE非常敏感,假設流經R1、R2的電流分別為I1和I2: • 當V1比V2稍大一點(V1V2> 0.1V),所有電流幾乎都被I1拿走: • 當V1比V2稍小一點(V2 V1 > 0.1V),所有電流幾乎都由I2分走:

此處兩顆BJT工作在active mode或cutoff mode,故有極快的切換速度。 • Vo由兩個輸入電壓差(V1 – V2 )所決定,而更重要的是:輸出端的高低電壓差(VH VL =IoR2)是由電流源及電阻決定,而非由電晶體的VCE所決定。

RC1 RC2 245 220 Q4 Vo R1 907 Q3 VR Vi Q1 Q2 D1 R3 6.1K D2 RE 779 R2 VEE(5.2V) • ECL反相器 • (Q1,Q2,RC1,RC2,RE)所組成的差動對是主要電路。 • (Q3,D1,D2,R1,R2,R3)是提供參考電壓VR的輔助電路。 • Q4則是為了提供穩定輸出電壓的輔助電路。 • ECL採用負電源(0V/5.2V),以此可有效降低雜訊影響。 4.98K

4.98K VC1 0V(高電位) RC1 RC2 245 220 Q4 Vo R1 907 Q3 VR Vi Q1 Q2 D1 R3 6.1K D2 RE 779 R2 VEE(5.2V) ECL邏輯電路 • ECL反相器—主要利用Q1、Q2組成的差動電路來達成。Vi是輸入電壓而VR是固定的參考電壓 。 • 假設Io為流經RE的電流: • 當ViVR > 0.1V,所有電流幾乎都流向Q1: • 當VR Vi > 0.1V,所有電流幾乎都流向Q2: Io = IE1 + IE2 IC1+ IC2 VC1 = IC1 RC1 (低電位)