8. The microprocessor

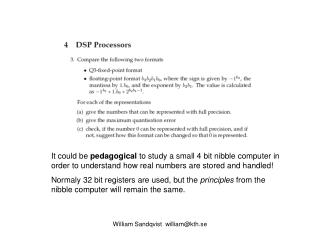

8. The microprocessor. Objective: To know and understand The microprocessor ( CPU ) A general cycle of instruction RTL: the register transfer language Principal modes of addressing of Motorola MC68000. A real instruction set: MC68000 An example of simulator: TC2111.

8. The microprocessor

E N D

Presentation Transcript

8. The microprocessor • Objective: To know and understand • The microprocessor (CPU) • A general cycle of instruction • RTL: the register transfer language • Principal modes of addressing of Motorola MC68000. • A real instruction set: MC68000 • An example of simulator: TC2111

8.1 The microprocessor • John von Neumann (1903-1957) • A brilliant idea… • The data AND the programs are coded in the same way, into binary, in order to be treated automatically by a machine (computer). • Architecture and instruction cycles at the origin of the sequential machines and microprocessors (CPU) of today.

M MAR É M O MDR I R E OpCode OpAddr A P RW DS R I N PC C I Control P HZN A ALU L E Example of architecture (TC2111) Mem. Data Register Operation code Operator address Mem. Addr. Register Accumulator Read Write Data Size Program Counter state ALU

Decoding • Used to differentiate various types of instructions of the CPU • Arithmetic instructions • Logical instructions • Transfer instructions • Branch instructions • Control instructions of the processor

Code Address Code Data Code Address 1 Address 2 Decoding • The instructions contain fields. Several formats, determined by the fields (codes can coexist in an instruction set). For example: • Format 1 • Format 2 • Format 3 • Format 4 Code

JMP $0123 Code Address ADD $01 Code Data MOVE $0123 $0200 Code Address 1 Address 2 Decoding - Example • HALT - Stopping of the processor • JUMP - Goes to address $0123 for the next instruction • ADD - Add 1 to the value of the temporary register • MOVE - Move the contents of the memory register $0123 towards the memory register $0200 HLT Code

Instruction Cycle Example with TC2111. The microprocessor repeats this cycle forever: 1- Fetch (loading) of the instruction (OpCode) 2- Decoding of the instruction 3- Fetch of the operands (if necessary)3.1 If in memory, then go to read them from memory 4- Execution of the operation (if necessary) 4.1 If ALU is needed, then carry out it in ALU 5- Storage of the results (if necessary) 5.1 If in memory, then go to write them in memory 6- Interruption present? (not in TC2111) 6.1 If so, then transfer of control towards the appropriate interruption routine.

M É M O I R E P R I N C I P A L E Instruction Cycle: Example. Current State MAR Program $002E: ... $0030: ADD$0032: $0036$0034: HLT$0036: $0001 $0038: ... MDR A=$05 OpCode OpAddr RW DS PC=$30 Control HZN ALU PC (Program Counter) = $0030, A = $0005

M É M O $0099 I R E ADD P R I N C I P A L E Instruction Cycle: Stage 1: Fetch of the instruction MAR = $0030, PC = $0030 $0030 Program $002E: ... $0030: ADD$0032: $0036$0034: HLT$0036: $0001 $0038: ... A=$05 OpAddr RW DS PC=$32 Control HZN ALU MDR = $0099 (ADD), OpCode = $0099, PC = $0032Stage 2: Decoding. $0099 = ADD, need for an operand.

M É M O I R E P R I N C I P A L E Instruction Cycle: Stage 3: Fetch of the operand MAR = $0032, PC = $0032 $0032 Program $002E: ... $0030: ADD$0032: $0036$0034: HLT$0036: $0001 $0038: ... $0036 ADD $0036 A=$05 RW DS PC=$34 Control HZN ALU MDR = $0036, OpAddr = $0036, PC = $0034

M É M O I R E P R I N C I P A L E Instruction Cycle: Stage 4: Execution of the instruction Fetch the value inALU. MAR = $0036, A = $0005 $0036 Program $002E: ... $0030: ADD$0032: $0036$0034: HLT$0036: $0001 $0038: ... $0001 ADD $0036 A=$06 RW DS PC=$34 Control HZN ALU MDR = $0001, A = A + MDR = $0006

M É M O I R E P R I N C I P A L E Instruction Cycle: Stage 5: Storage of the result The result is already in A. No storage here. $0036 Program $002E: ... $0030: ADD$0032: $0036$0034: HLT$0036: $0001 $0038: ... $0001 ADD $0036 A=$06 RW DS PC=$34 Control HZN ALU Pass to the next instruction (start the cycle again !). To store A in memory (addresses $0050), the next instruction should be STA $0050.

M É M O I R E P R I N C I P A L E Control unit and status bits MAR MDR OpCode OpAddr A RW DS PC Control HZN ALU

Realization of the control unit • Two ways: • Hardware • Synchronous sequential circuit • Powerful • Complex and expensive design • Difficult to modify • Microprogramming • Design less complex and easier to modify but less powerful • Control memory

Microcoding Instruction (Machine language) CPU microprograms micro-instructions Control unit

Register transfer language (RTL) • Allows to describe the microinstructions and their micro-operations. • Example. Addition (ADD) carries out the following functionality: A := A + MDR(where MDR contains the value to be added) 1) A A + MDR 2) N An-1 (where An-1is the most significant bit of A)

8.2 Addressing Modes • Rules to access the operands • in memory, • in a register, • in the instruction itself. • Considerations • To increase the flexibility and the facility of programming • To decrease the length of the generated code • Successive accesses to the operands (lists…)

Motorola MC68000 - Structure • The MC68000 (Motorola, 1979) is a processor that has: • 8 data registers (D0 with D7) of 32 bits • 8 address registers (A0 with A7) of 32 bits • A PC register (Program Counter) • A status register containing the status bits such as VCNZX • Several different way of addressing

Motorola MC68000 - Memory • Accessible memory: • 16 MB • Addresses on 24 bits, therefore they go from $000000 to $FFFFFF. • The data in memory are expressed by words (2 octets or 1 word). • The length of the data is indicated by the letters B (1 octet - byte), W (a word of 2 octets - word) and • L (length-word of 4 octets - long word).

Octet Octet $FFFFFE Word $FFFFFC . . . . . . Long $000004 word $000002 Word $000000 Motorola MC68000 - Memory $00 $FF $ABCD . . . $01234567 $1234

Notation RTL for assembler 68000 & description of the modes • Ai Address register(i = 0..7) • Di Data Register (i = 0..7) • Xi Data or address register (i = 0..7) • d8Signed displacement of 8 bits (-128..127) • d16Signed displacement of 16 bits (-32768…32767) • d32Signed displacement of 32 bits (-2G…2G) • eaActual address (effective address) • < >Necessary parameter (often source or destination) • [x]Contents of X • [M(x)]Contained memory with address X • 10 (10)10 • $10 (10)16 • %10 (10)2 • ‘10’ “10”ASCII

Several modes of addressing… • MC68000 (EA = effective address) : • Implicit (particular register (i.e. PC)) • Immediate (constant) • Register (register specific) • Direct (explicit EA) • Indirect-memory (EA=[address report ]) • Indirect-register (EA = [ register ]) • Relative (EA = base register +offset) • Indexed (EA = offset + register index)

Immediate addressing • The operand is a constantNotation: #constant • MOVE.B #$10, D5 (D5.B := $10) other bits of D5: unchanged • MOVE.W #1024, D5 (D5.W := $0400)

Absolute Address • The operand is [ M(ea) ]Notation: ea • MOVE.B $1000, D5 (D5.B := [M($001000)] ) • MOVE.L #$1234, $1234 ( [M($001234)] = $1234 )

Direct addressing by register • ea = Xiand the operand is ea • Notation: Ai or Di • MOVE.W A4, D5 (D5.W = A4.W) • MOVE.L #$1234, D1 (D1 = $0000 1234)

Indirect addressing by register • ea = [Ai]and the operand is [ M(ea) ]Notation: (Ai) • MOVE.B (A4), D5 (D5.B = M([A4]) ) • MOVE.L #$1234, (A1) (M([A1]) = $0000 1234)

Indirect addressing by register with post-increment • ea = [Ai]and the operand is [ M(ea) ] Notation: (Ai)+ • If .B thenAi [Ai] + 1 after the execution of the instruction • If .W then Ai [Ai] + 2 after the execution of the instruction • If .L then Ai [Ai] + 4 after the execution of the instruction • MOVE.B (A0)+, D3 • MOVE.W (A4)+, (A5)+ • MOVE.L #$1234, (A1)+

Indirect addressing by register with pre-decrement • ea = [Ai] - 1, 2 or 4 The operand is [ M(ea) ]Notation: -(Ai) • If .B then Ai [Ai] - 1 before the execution of the instruction • If .W then Ai [Ai] - 2 before the execution of the instruction • If .L then Ai [Ai] - 4 before the execution of the instruction • MOVE.B -(A0), D3 • MOVE.W -(A4), (A5)+ • MOVE.L #$1234, -(A1)

Indirect addressing by register with displacement • ea = d16 + [Ai], the operand is [ M(ea) ]Displacement is a 16 bits number in 2CF extended to 32 bits • Notation: d16 (Ai)(where d16 is signed and extended to 32 bits)Ai remains UNCHANGED. • MOVE.L 12(A4), D3 • MOVE.B $FFFF(A4), D3

Indirect addressing by register with displacement (II) • MOVE.L 12(A4), D3 (D3.L := [ M( [A4] + ($0000 000C)16 ) ]because 12 in 16 bits = $000C, and thus its 32 bits representation is $0000 000C.A4 is not modified. • MOVE.B $FFFF(A4), D3 (D3.B := [ M( [A4] + ($FFFF FFFF)16 ) ]because $8000 on 16 bits is negative, and thus its 32 bits representation is $$FFFF>FFFF (-1!).

Indirect addressing by register with index • ea = d8 + [Ai] + [Xi]The operand is [ M(ea) ]Displacement is a 8 bits number in 2CF extended to 32 bits • Notation: • d8 (Ai, Xi.W) where Xi.W is signed and extended to 32 bits, or • d8 (Ai, Xi.L) • Example: MOVE.L 9(A1, D0.W), D3

Indirect addressing by register with index (II) • MOVE.L 9(A1, D0.W), D3 [D3] := [ M( [A1] + ($???? [D0.W]) + ($0000 0009)16 )]where???? is worth 0000 or FFFF according to the sign of D0.W • MOVE.L $FF(A1, D0.W), D3 [D3] := [ M( [A1] + ($???? [D0.W]) + ($FFFF FFFF)16 )]notice that $FFFF FFFF = -1 !!!

Exercises: Addressing modes Registers ( [Xi] = content ): Memory ( [address] = content ): [A0] = $0000 2000 [$002000] = $1234 [A1] = $0000 2004 [$002002] = $5678 [D0] = $1266 6565 [$002004] = $BEAD [D1] = $AAAB B2DD [$002006] = $F00D [D2] = $100A 0005 ... [D3] = $ABCD 573D [$00200C] = $A110 MOVE.? #$20, D0 With .B With .W With .L [D0] =

Exercises: Addressing modes Registers ( [Xi] = content ): Memory ( [address] = content ): [A0] = $0000 2000 [$002000] = $1234 [A1] = $0000 2004 [$002002] = $5678 [D0] = $1266 6565 [$002004] = $BEAD [D1] = $AAAB B2DD [$002006] = $F00D [D2] = $100A 0005 ... [D3] = $ABCD 573D [$00200C] = $A110 MOVE.? #$20, D0 With .B With .W With .L [D0] = $1266 6520 $1266 0020 $0000 0020

Exercises: Addressing modes MOVEA.? #$20, A1 [A1] = Prohibited. $0000 0020 $0000 0020 MOVE.? D0, D1 [D0] = $AAAB B265 $AAAB 6565 $1266 6565 MOVEA.? D1, A0 [A0] = Prohibited. $FFFF B2DD $AAAB B2DD

Exercises: Addressing modes MOVE.? (A0), D3 [D3] = $ABCD 5712 $ABCD 1234 $1234 5678 MOVEA.? (A1), A4 [A4] = Interdit. $FFFF BEAD $BEAD F00D MOVE.? D0, (A0) [$002000] = $6534 $6565 $1266 [$002002] = $5678 $5678 $6565

Exercises: Addressing modes MOVE.? $2(A0), D0 [D0] = $1266 6556 $1266 5678 $5678 BEAD MOVE.? (A1)+, D3 [D3] = $ABCD 57BE $ABCD BEAD $BEAD F00D [A1] = $0000 2005 $0000 2006 $0000 2008 MOVE.? D3, (A1)+ [$002004] = $3DAD $573D $ABCD [$002006] = $F00D $F00D $573D [A1] = $0000 2005 $0000 2006 $0000 2008

Exercises: Addressing modes MOVE.? -(A1), D3 [A1] = $0000 2003 $0000 2002 $0000 2000 [D3] = $ABCD 5778 $ABCD 5678 $1234 5678 MOVE.? D3, -(A1) [A1] = $0000 2003 $0000 2002 $0000 2000 [$002000] = $1234 $1234 $ABCD [$002002] = $563D $573D $573D

Exercises: Addressing modes MOVE.? $3(A1, D2.W), D0(suppose [$00200E] = $9876) ea = $0000 0003 + $0000 2004 + $0000 0005 = $0000 200C [D0] = $1266 65A1 $1266 A110 $A110 9876 MOVE.? $2000, $2004 [$002004] = $12AD $1234 $1234 [$002006] = $F00D $F00D $5678

8.3 Instruction set • Set of instructions in machine language of a processor • Transfer instructions • Arithmetic instructions • Logical instructions • Branch instructions • Control instructions of the processor • Example: MC68000

Transfer instructions • MOVE, MOVEA, LEA, EXG, SWAP. • [D0] = $1234 5678, [A3] = $ABCD EF90 • SWAP Dn: The right word and the left word of Dnare swapped. • SWAP D0 : [D0] = $5678 1234 • EXG Rn,Rn: The contents (long-words, therefore 32 bits) of the two registers are swapped (EXchanGe). • EXG D0, A3 : • [D0] = $ABCD EF90 [A3] = $1234 5678

Arithmetic instructions • ADD, SUB, MULU, DIVU, ... • These instructions affect usually the bits XNZVC register CCR (Condition Codes Register): • X : Extended (often, same result as C) • N : Negative • Z : Zero • V : Overflow • C : Carry

Arithmetic instructions - Addition • [D1] = $2233 4455, [D3] = $1234 5678 • ADD.B D3, D1($55 + $78 = $CD) • [D1] = $2233 44CD • XNZVC =01010 • (Overflow because the sign of the result (-) is different from that of the operands (+))

Arithmetic instructions - Addition • [D1] = $2233 4455, [D3] = $1234 5678 • ADD.W D3, D1 [D1] = $2233 9ACD XNZVC = 01010 (Overflow) • ADD.L D3, D1 [D1] = $3467 9ACD XNZVC = 00000 (No overflow)

Arithmetic instructions - Addition • [D0] = $2C34 C11C, [A0] = $0112 B33C • ADDA.L D0, A0 [A0] = $2D47 7458 • ADDA.W D0, A0 ([A0] + $C11C extended($FFFF C11C)) [A0] = $0112 7458 • ADD.W A0, D0 [D0] = $2C34 7458

Arithmetic instructions - Addition • Other instruction of addition exist : • ADDI: To add the immediate data • ADDQ: Add Quick, to increment with the 4 bits data • ADDX: To add with extension • ABCD: Addition of BCD numbers • Subtraction: Like the addition, but key word ADD is replaced by SUB • (SUB, SUBA, SUBI, SUBQ, SUBX, SBCD).

Arithmetic instructions - Multiplication • Only with words of 16 bits. • MULU <ea>,Dn (multiplication unsigned) • MULS <ea>,Dn (multiplication signed) • [D0] = $1234 A678 [D1] = $A012 0002 • MULU D0, D1 • [D1.L] = [D0.W] x [D1.W] • [D1] = $A678 x $0002 = $0001 4CF0

Arithmetic instructions - Multiplication • [D2] = $336B 4105 [D3] = $B11C A024 • MULU D2, D3 • [D3] = $4105 x $A024 = $28AC 44B4 • X = 0 • N = 0 • Z = 0 • V = 0 (because MULU unsigned). • C = 0

Arithmetic instructions - Division • 32 bits / 16 bits = 16 bits, reste 16 bits. • DIVU <ea>,Dn (unsigned division) • DIVS <ea>,Dn (signed division) • There are potential dangers…? • [D2] = $28AC 44B5 [D3] = $1C32 A024 • DIVU D3, D2 • MSW([D2.L]) = [D2.L] MOD [D3.W] • LSW([D2.L]) = [D2.L] DIV [D3.W] • [D2] = $0001 4105 (remainder, quotient)