ECE 371 – Unit 15

600 likes | 743 Views

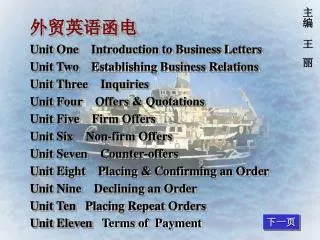

ECE 371 – Unit 15. • Data Acquisition Systems • A/Ds in MC9S12DPS56B Microcontroller. Data Acquisition Systems. Overview. Data Acquisition System. Mux. Programmable Amplifier. Sample Hold Amplifier. A/D. Select Gain. Pacer Clock. Select Input Channel. Single Ended Input.

ECE 371 – Unit 15

E N D

Presentation Transcript

ECE 371 – Unit 15 • Data Acquisition Systems • A/Ds in MC9S12DPS56B Microcontroller

Data Acquisition Systems Overview

Data Acquisition System Mux Programmable Amplifier Sample Hold Amplifier A/D Select Gain Pacer Clock Select Input Channel

Single Ended Input • 1 Switch in Multiplexer per Input • Common Ground • Potential Ground Loop Problems • Inputs may not share a common ground • Can be source of noise

Differential Input 2 Switches per Input Eliminates Ground Loops

Multiplexer • Most Data Acquisition Systems allow user to select either 2N Single Ended or N Differential Inputs by Jumper • They usually quote number of Single Ended Inputs since it is larger number

Programmable Amplifier • Gain is Selectable by Computer • Improves Accuracy of Conversion • By Selecting Gain, can Delete Leading Zero and provide more significant digits in result

Track Store – Sample Hold Amplifier • In Track or Sample mode, output of amplifier tracks replicates the amplifier input. • Switch to Store or Hold, Output of amplifier stays constant at last track/sample input

Pacer Clock • Can be used to determine the sampling rate of AD • Each tick initiates AD conversion. • End of conversion options: • Raise Flag to be sampled by software • Generate Interrupt • Transfer via Direct Memory Access to Memory Buffer

A/D Converter in MC9S12DP256B Microcontroller

MC9S12DP256B - A/D Converter Parameters • VMAX = Vrh = 5.0 Volts Typical • VMIN = Vrl = 0.0 Volts Typical • Range = VMAX - VMIN • VMIN ≤ Vin ≤ VMAX • Resolution • 10 bit: Resolution = Range/1024 • 8 bit: Resolution = Range/256

MC9S12DP256B A/D Overview • Analog/Digital with Input Multiplexing • Input Pin can be Digital Input • Input Pin can be Analog Input • 8 Channel Analog Input Multiplexer per A/D • 8/10 bit Resolution • Left/Right Justified • Signed/Unsigned Result • 7 usec, 10-bit Single Conversion Time • Sample Buffer Amplifier • Programmable Sample Time

MC9S12DP256B A/D Overview • External Trigger Control Option • Start Conversion with External Signal • Conversion Complete Interrupt Option • 1 to 8 Conversion Sequence Lengths • Select 1 to 8 Conversions on Start • Continuous Conversion Mode • Multiple Scans • Scan Several Channels on Start Command

Channel 0 Symbol Definitions #define ATD0CTL0 _P(0x80) // ADC control 0 (reserved) #define ATD0CTL1 _P(0x81) // ADC control 1 (reserved) #define ATD0CTL2 _P(0x82) // ADC control 2 #define ATD0CTL3 _P(0x83) // ADC control 3 #define ATD0CTL4 _P(0x84) // ADC control 4 #define ATD0CTL5 _P(0x85) // ADC control 5 #define ATD0STAT _LP(0x86) // ADC status register hi #define ATD0TEST _LP(0x88) // ADC test (reserved) #define ATD0DIEN _P(0x8D) //

#define PORTAD _P(0x8F) // port ADC = input only #define ADR00H _P(0x90) // ADC result 0 register high byte #define ADR00L _P(0x91) // ADC result 0 register low byte #define ADR01H _P(0x92) // ADC result 1 register #define ADR01L _P(0x91) // ADC result 1 register low byte #define ADR02H _P(0x94) // ADC result 2 register #define ADR02L _P(0x91) // ADC result 2 register low byte #define ADR03H _P(0x96) // ADC result 3 register #define ADR03L _P(0x91) // ADC result 3 register low byte #define ADR04H _P(0x98) // ADC result 4 register #define ADR04L _P(0x91) // ADC result 4 register low byte #define ADR05H _P(0x9A) // ADC result 5 register #define ADR05L _P(0x91) // ADC result 5 register low byte #define ADR06H _P(0x9C) // ADC result 6 register #define ADR06L _P(0x91) // ADC result 6 register low byte #define ADR07H _P(0x9E) // ADC result 7 register #define ADR07L _P(0x91) // ADC result 7 register low byte

Channel 0 -16-bit Result Register Definitions #define ATD0DR00H _LP(0x90) // ADC result 0 register #define ATD0DR01H _LP(0x92) // ADC result 1 register #define ATD0DR02H _LP(0x94) // ADC result 2 register #define ATD0DR03H _LP(0x96) // ADC result 3 register #define ATD0DR04H _LP(0x98) // ADC result 4 register #define ATD0DR05H _LP(0x9A) // ADC result 5 register #define ATD0DR06H _LP(0x9C) // ADC result 6 register #define ATD0DR07H _LP(0x9E) // ADC result 7 register

Input Selection – Digital or Analog IENx = “1” – Input is Digital IENx = “0” – Input is Analog ATDDIEN = 0x5A; // Channels 6, 4, 3, 1 are Digital

8 16-bit Result Registers • Option of 8 or 10 bit Conversions • SRES8 – ATDCTL4 • “1” – 8-bit conversions • “0” – 10-bit conversions • Left or Right Justified Data • DJM – ATDCTL5 • “1” – Right Justified • “0” – Left Justified • Signed or Unsigned • DSGN – ATDCTL5 • “1” – Signed Result • “0” – Unsigned Result

Example: 0 - 5 Volt Input Range • Left Justified (DJM = 0) • Unsigned (DSGN = 0) • 3.75 V = 0b1100 0000 0000 0000 For 10-bit case, un-used • 2.5 V = 0b1000 0000 0000 0000 bits are “0” • 1.25 V = 0b0100 0000 0000 0000 For 8-bit case, low byte is undefined • 0.00 V = 0b0000 0000 0000 0000 • Signed (DSGN = 1), • 3.75 V = 0b0100 0000 0000 0000 SRES = 1 -- 8-bits • 2.5 V = 0b0000 0000 0000 0000 SRES = 0 -- 10-bits • 1.25 V = 0b1100 0000 0000 0000 • 0.00 V = 0b1000 0000 0000 0000

Example: 0 - 5 Volt Input Range (cont) • Right Justified (DJM = 1), 10-bit Outputs • Unsigned (DSGN = 0) • 3.75 V = 0b0000 0011 0000 0000 • 2.5 V = 0b0000 0010 0000 0000 SRES8 = 0 -- 10-bits • 1.25 V = 0b0000 0001 0000 0000 • 0.00 V = 0b0000 0000 0000 0000 • Signed (DSGN = 1), 10-bit Outputs • 3.75 V = 0b0000 0001 0000 0000 Unused left 6 or 8 • 2.5 V = 0b0000 0000 0000 0000 Bits are “0” • 1.25 V = 0b0000 0011 0000 0000 Does not Sign Extend • 0.00 V = 0b0000 0010 0000 0000 2’s Complement

ATD Control Register 4 • ATD Clock Pre-scaler • ATD Clock = .5*BusClock/(PRS+1) • PRS = PRS4,PRS3,PRS2,PRS1, PRS0 • Example PRS=0 • PRS4=0,PRS3=0,PRS2=0, PRS1=0, PRS0=0 • Example – All bits = 1 PRS=31 • 8 to 10 Bit A/D Resolution Selection

Two Clock Phases • Phase One (2 Clock Cycles): Analog Input Connected via Amplifier to Capacitor to Rapidly Charge Capacitor rapidly to Analog Input Voltage • Phase Two (2, 4, 8 or 16 Clock Cycles-selectable): Connect Analog Input Directly to Capacitor for Final Charging and High Accuracy

ADTCTL4 Example ADTCTL4 = 0x24; // 0b0 01 00100 Bit 7 – 10-bit conversion accuracy Bit 6,5 – 4 ATD Clocks for Phase 2 of Sampling Bits 4-0 – ATD Clock Divisor ATD Clock Freq = 2,000,000*(1/2)*(1/(4+1)) = 200,000 Hertz ATD Clock Period = 5 usec 2 Clocks for Phase 1 of Sampling 4 Clocks for Phase 2 of Sampling 10 Clocks for Conversion 16 Clocks * 5 usec = 80 usec = Conversion Time

ATDCTL5 - Example /* Left Justified, Unsigned, Single Conversion Sequence One Channel = Channel 3 DJM=0, DSGN=0, SCAN=0, CC,CB,CA= 011 */ ATDCTL5 = 0x03; //This is how a conversion sequence is Initiated by software

ATDCTL2 - Example • ATD0CTL2 = 0x80; // Enable Unit 0 • ADPU = 1 – Turn on AD • AFFC = 0 – Normal Flag • ETRIGLE = 0 – Used with external triggering • ETRIGP = 0 – Used with external triggering • ETRIGE = 0 – Not external triggered • ASCIE = 0 – Disable AD Interrupts • Bit 0 – Not used on write

#define ATD0CTL0 _P(0x80) #define ATD0CTL1 _P(0x81) #define ATD0CTL2 _P(0x82) #define ATD0CTL3 _P(0x83) #define ATD0CTL4 _P(0x84) #define ATD0CTL5 _P(0x85) #define ATD0STAT0 _P(0x86) #define ATD0STAT1 _P(0x8B) #define ATD0DIEN _P(0x8D) #define PORTAD0 _P(0x0F)

#define ATD0DR0H _P(0x90) #define ATD0DR0L _P(0x91) #define ATD0DR1H _P(0x92) #define ATD0DR1L _P(0x93) #define ATD0DR2H _P( 0x94) #define ATD0DR2L _P( 0x95) #define ATD0DR3H _P( 0x96) #define ATD0DR3L _P( 0x97) #define ATD0DR4H _P( 0x98) #define ATD0DR4L _P( 0x99) #define ATD0DR5H _P( 0x9A) #define ATD0DR5L _P( 0x9B) #define ATD0DR6H _P( 0x9C) #define ATD0DR6L _P( 0x9D) #define ATD0DR7H _P( 0x9E) #define ATD0DR7L _P( 0x9F)

ATD Example A • All Channels are Analog Inputs • ATD0DIEN = 0x00; ATD0DIEN IEN6 IEN7 IEN6 IEN5 IEN4 IEN3 IEN2 IEN6 IEN1 IEN0 1: DIGITAL INPUT 0: ANALOG INPUT

ATD Example A • Enable AD, No external trigger, No interrupt • ATD0CTL2=0x80; ATD0CTL2 ASCIF ADPU AFFC ETRIGLE ETRIGEP ADPU AWAI ETRIGE ASCIE

ATD Example A • 10 bits, Min S/H Setup, Fastest Clock • ATD0CTL4 = 0x00; ATDCTL4 SMP0 SRES8 SMP1 PRS4 PRS3 PRS2 PRS1 PRS0

ATD Example A • Sequence Length = 1 (1 Conversion) , No FIFO • ATD0CTL3 = 0x08; ATDCTL3 0 S8C S2C S1C FRZ2 S4C FIFO FRZ1

ATD Example A • Right Justified, Unsigned, Single Conversion Sequence, Channel 3 only • ATD0CTL5 = 0x03; // Starts Conversion ATD0CTL5 0 CC CB CA DJM DSGM SCAN MULT