BUS IN MICROPROCESSOR

BUS IN MICROPROCESSOR. Topics to discuss Bus Interface ISA VESA local PCI Plug and Play. Bus Interface ISA (Industry Standard Architecture) VESA local bus (Video Electronics Standards Association) PCI (peripheral component interconnect). BACK.

BUS IN MICROPROCESSOR

E N D

Presentation Transcript

Topics to discuss • Bus Interface • ISA • VESA local • PCI • Plug and Play

Bus Interface • ISA (Industry Standard Architecture) • VESA local bus • (Video Electronics Standards Association) • PCI (peripheral component interconnect) BACK

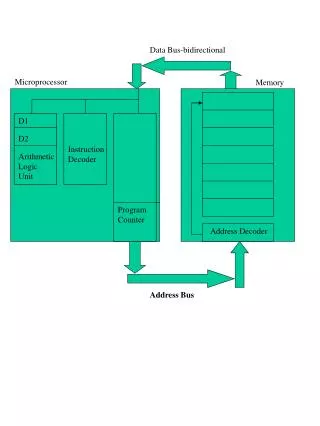

Detail pin connections and signal connections on the ISA, VESA local, and PCI buses. • Develop simple interfaces to the ISA, VESA local and PCI buses. • Program interface places on boards that connect to the ISA, VESA local, and PCI buses. • Describe operation of the USB and develop some short programs that transfer data. • Explain how the AGP increases the efficiency of the graphics subsystem.

ISA • Been around since the start of the IBM PC (1982) • Originally an 8-bit standard, now 16-bit. There was a 32-bit EISA (Extended), gone • Most PCs have an ISA slot on the mainboard that can accept either an 8-bit of a 16-bit ISA printed circuit card. • 32-bit printer circuit cards are more often PCI, or in some older 486s, the VESA cards. BACK

ISA / EISA / VESA local • Clocking speed 8 MHZ too slow!! • EISA -32-bit modification of ISA (386-PentiumII had 32-bit data buses) • Both ISA and EISA run at 8 MHz • too SLOW! • VESA and PCI both run at 33 MHz. • Most common application for EISA bus is as a disk controller or as a video graphics adapter. Both apps benefit from the wider bus width because the data transfer rates for these devices are high.

VESA local • Much better approach to 32-bit interfacing • Common for video and disk interfaces to the 486 PC BACK

PCI • PCI -Peripheral Component Interconnect • Only bus found in the newest Pentium II systems. (Most systems also have ISA, but as an interface for older 8-bit and 16-bit interface cards). • Has replaced VESA bus. • Has plug and play(PnP) characteristics • Has the ability to function with a 64-bit data bus. • Most often used for interfacing I/O components • Memory could be interfaced, but would operate only at a 33MHz rate with Pentium (half the speed of the redient local bus of the Pentium) BACK

Plug and Play • PCI interface contains a series of registers, located in a small memory device on the PCI interface, that contain information about the board. • This memory can provide PnP characteristics to the ISA bus or any other bus. • Information in registers allows computer to automatically configure the PCI card. BACK

PCI Bridge • Not just buffers between PCI and processor busses. INTELLIGENT! • Capable of grouping single data requests into bursts and then exchanging those bursts with memory and I/O devices. • Ability to transfer an unlimited number of bytes in a single burst – even though processor itself may be limited to a much smaller size (one cache line) • Each PCI device has a latency timer that defines longest time that device is allowed to control the bus.

PCI Bus Operation • The data bus lines use a multiplexing scheme to which connector pins are multiplexed as address and data pins. • A PIC transaction takes place between a master (a device takes control of the system buses), and a target (a device that only responds to access requests).

BUS Access • Read cycle takes three clock pulses • Output address • Switch lines from address to data • Transfer data • Write cycle • Address lines do not have to turned around • Only requires two clock cycles.

Bus Commands • 16 different commands (commands are multiplexed on the C/BE3’-C/BE0’) lines and output during the address phase of each bus cycle. • INTA sequence • I/O read access • I/O write access • Memory read access • Memory write access • Dual addressing cycle (64 bits on 32-bit data bus) • Line memory read access (line of cache (greater than 32 bits)