Xilinx CPLD kola

340 likes | 537 Views

Xilinx CPLD kola. XC9500 serija CoolRunner™ serija. Goran Mi šić, 12103. Šta je CPLD kolo ?. CPLD kolo je kombinacija potpuno programab ilnih AND/OR mreža i blokova makroćelija . AND/OR mreža je reprogramab ilna ; obavlja mnoštvo kombinacionih logičkih funkcija .

Xilinx CPLD kola

E N D

Presentation Transcript

Xilinx CPLD kola XC9500 serija CoolRunner™ serija Goran Mišić, 12103

Šta je CPLD kolo? • CPLD kolo je kombinacijapotpuno programabilnih AND/OR mreža i blokova makroćelija. • AND/OR mrežaje reprogramabilna; obavlja mnoštvo kombinacionih logičkih funkcija. • Makroćelije su funkcionalni blokovisa kombinaciono/sekvencijalnom logikom; pružaju dodatnu fleksibilnost u vidu mogućnosti izbora različitih povratnih veza i funkcije pripadajućih pinova.

Zaštokoristiti CPLD? • Zahvaljujući jedinstvenim mogućnostima CPLD kola, njihovo korišćenje pri projektovanju digitalnih sistema pruža čitav niz prednosti: • Reprogramabilnost - sistem se moze rekonfigurisati gotovo proizvoljan broj puta; mogućnost poboljšavanja i otklanjanja grešaka; izmena projekta je brza, jeftina, u bilo kom trenutku i sa bilo kog mesta • Jednostavnost - jednostavnokorišćenje, brzo, lako i jeftino projektovanje • NV memorija - programirana funkcija se ne gubi pri prestanku napajanja i dostupna je odmah posle uključenja • Ekonomičnost - niska cena; mali broj dodatnih komponenti; manja, jednostavnija i jeftinija štampana pločica

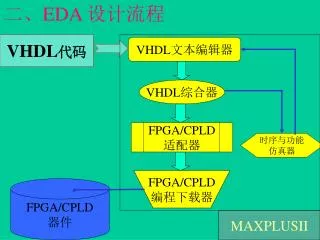

Projektovanje pomoću CPLD kola • Korak 1: izbor odgovarajućeg kola prema sledećim kriterijumima: • Logički kapacitet • Performanse (brzina) • Napon napajanja i potrošnja • Pakovanje (dimenzija čipa i potreban broj pinova) • Korak 2: izbor odgovarajućeg softvera • Prema obimu i zahtevima projekta determinisati potreban softver. Za bazično projektovanje je dovoljan besplatni ISE WebPACK (http://www.xilinx.com/ise/logic_design_prod/webpack.htm) • Korak 3: implementacija projekta • Projektovanje i simulacija (testiranje) sistema pomoću softvera • Programiranje (potreban je JTAG programator) i testiranje prototipa • Pisanje odgovarajuće projektne dokumentacije

Serija XC9500 - karakteristike • Visoke performanse • Veliki raspon logičkog kapaciteta • 5V "in-system programmable" (ISP) čipovi • minimalno 10,000 ciklusa programiranja/brisanja • Poboljšana "pin-locking" arhitektura • Flexibilni 36in/18out programabilni logički blokovi • 90 članova proizvoda (product terms - PT) vezana su za bilo koju ili svih 18 makroćelija • Globalni and PT clock, dozvola izlaza (output enable), set i reset signali • Obimna podrška IEEE Std 1149.1 boundary-scan (JTAG) • Programabilni mod rada sa redukovanom potrošnjom za svaku makroćeliju • Slew rate kontrola na pojedinačnim izlazima • Mogućnost programiranja prinova za masu • Poboljšana mogućnost bezbednosti i zaštite projekta • Velika struja izlaza (24 mA) • 3.3V ili 5V I/O • Napredna CMOS 5V FastFLASH™ tehnologija • Podrška paralelnom programiranju više XC9500 kola

Serija XC9500 - makroćelija unutar programabilnog logičkog bloka

Serija XC9500 - veza makroćelija sa pinovima Clock i Set/Reset

Serija XC9500 - PT alokator PT alokator Primer kombinovanja parcijalnih suma proizvoda više makroćelija

Serija XC9500XL/XV - karakteristike Sem standardnih osobina, čipove iz ove serije karakteriše: • Optimizovani su za 3.3V (XL) / 2.5V (XV) sisteme visokih performansi • Smanjena potrošnja • Višenaponski način rada • Flexibilni 54in/18out programabilni logički blokovi • Do 90 članova proizvoda (PT) po makroćeliji sa pojedinačnom PT alokacijom • Lokalna Clock inverzija sa tri globalna i jednim PT Clock-om • Bus-hold kolo na svim korisničkim pinovima • Izuzetan kvalitet i pouzdanost • Minimalno 10,000 ciklusa programiranja/brisanja • Čuvanje podataka 20 godina • ESD zaštita premašuje 2000V • Čipovi su pin-kompatibilni sa drugim čipovima iz iste serije

Serija XC9500XL/XV - makroćelija unutar programabilnog logičkog bloka

Serija XC9500XL/XV - veza makroćelija sa pinovima Clock i Set/Reset

Serija CoolRunner XPLA3 • Fast Zero Power™ (FZP) tehnika projektovanja obezbeđujeultra-nisku potrošnju i vrlo visoku brzinu • Tipična standby struja je 17 do 18 μA na 25° C • Inovativna CoolRunner™ XPLA3 arhitektura kombinuje visoku brzinu i ekstremnu fleksibilnost • Napredni 0.35μ metal-petoslojni EEPROM proces • 1,000 ciklusa programiranja/brisanja • Čuvanje podataka 20 godina • 3V ISP korišćenjem JTAG IEEE 1149.1 interfejsa • 5V toleracija I/O pinova • Single pass logika proširiva do 48 članova proizvoda • Inovativna Control Term struktura obezbeđuje kompleksni asinhroni Clock • Asinhroni Clock, preset/reset i Clock enable makroćelija • Četiri kontrolaoutput enable po logičkom bloku • Foldback NAND za optimizaciju sinteze • Univerzalni 3-state koji olakšava testiranje

Serija CoolRunner XPLA3 - logički blok • Svaki logički blok sadrži PLA (programabilna i AND i OR mreza, koja generiše kontrolne i clock uslove) i logičke ćelije.Ulazi PLA su direktno vezani za ZIA.

Serija CoolRunner XPLA3 - multiplekser funkcija promenljivih (Variable Function Muliplexer - VMF) • VFM povećava logičku optimizaciju implementiranjem nekih dvoulaznih logičkih funkcija pre ulaska u makroćeliju

Serija CoolRunner XPLA3 - makroćelija • Svaka od makroćelija može obezbediti kominacionu ili sekvencijalnu logiku. Makroćelije se prilagođavaju asinhronom presetu/resetu i "power-on" inicijalnom stanju.

Serija CoolRunner-II • CPLD optimizovan za 1.8V sisteme • Najbrži CPLD sa malom potrošnjom • Najbolji CPLD sa 0.18 mikronskim CMOS-om • Višenaponski I/O rad (1.5V do 3.3V) • Napredne sistemske karakteristike • On-The-Fly rekonfiguracija (OTF) • Opcionalni Schmitt trigger ulaz (po pinu) • Višestruki I/O blokovi • Nenadmašno upravljanje malom potrošnjom • DataGATE spoljašna kontrola signala • Opcionalni DualEDGE trigerovani registri • Fleksibilni clock modovi • Clock delitelj (÷ 2,4,6,8,10,12,14,16) • CoolCLOCK • Višestruki globalni clock-ovi sa faznom selekcijom (po makroćeliji) • Višestruki globalni output enable • Globalni set/reset • PLA arhitektura • 100% PTrutabilnostkroz logičke blokove

Xilinx • Za prezentaciju je korišćen materijal koji se može naći na http://www.xilinx.com/ Goran Mišić, 12103