CPLD

DESCRIPTION

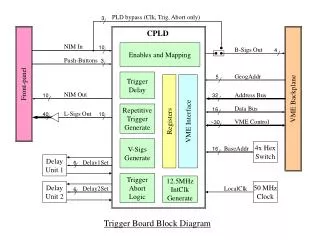

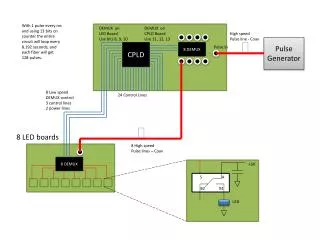

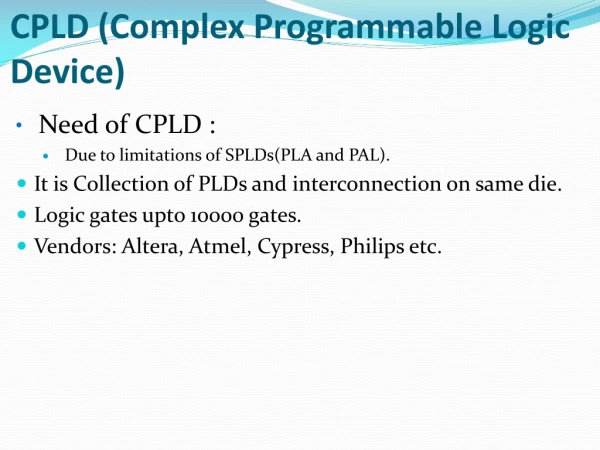

PLD bypass (Clk, Trig, Abort only). 3. Front-panel. CPLD. VME Backplane. NIM In. Enables and Mapping. 10. B-Sigs Out. 4. Push-Buttons. 3. Trigger Delay. GeogAddr. 5. Registers. VME Interface. NIM Out. Address Bus. 10. 32. Repetitive Trigger Generate. Data Bus. 16.

1 / 1

Download Presentation

CPLD

An Image/Link below is provided (as is) to download presentation

Download Policy: Content on the Website is provided to you AS IS for your information and personal use and may not be sold / licensed / shared on other websites without getting consent from its author.

Content is provided to you AS IS for your information and personal use only.

Download presentation by click this link.

While downloading, if for some reason you are not able to download a presentation, the publisher may have deleted the file from their server.

During download, if you can't get a presentation, the file might be deleted by the publisher.

E N D

Presentation Transcript

PLD bypass (Clk, Trig, Abort only) 3 Front-panel CPLD VME Backplane NIM In Enables and Mapping 10 B-Sigs Out 4 Push-Buttons 3 Trigger Delay GeogAddr 5 Registers VME Interface NIM Out Address Bus 10 32 Repetitive Trigger Generate Data Bus 16 L-Sigs Out 40 10 VME Control ~30 V-Sigs Generate 4x Hex Switch BaseAddr 16 Delay Unit 1 Delay1Set 6 Trigger Abort Logic 12.5MHz IntClk Generate Delay Unit 2 50 MHz Clock Delay2Set LocalClk 6 Trigger Board Block Diagram

More Related