5.3 8086 的中断系统

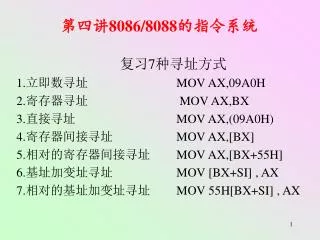

5.3 8086 的中断系统. 5.3.1 中断结构 采用中断矢量结构 , 每个中断有一个中断类型码 ( 号 ), 供 CPU 进行识别 , 最多能处理 256 种不同的中断类型 ( 即 256 个入口矢量 ). 一、中断向量表 存放中断服务程序入口地址的表格 . 结构如图 5-15 所示。存放在存储器的最低端,占用 0~3FFH ( 1024 个)字节的地址空间。. 构成:每个中断入口地址占 4 个字节,低 2 字节放入口地址的段内偏移量 IP ,高 2 字节放段基址 CS , 4 个单元的最低地址称为向量地址(中断向量)。 向量地址 = 中断类型码* 4

5.3 8086 的中断系统

E N D

Presentation Transcript

5.3 8086的中断系统 • 5.3.1 中断结构 • 采用中断矢量结构,每个中断有一个中断类型码(号),供CPU进行识别,最多能处理256种不同的中断类型(即256个入口矢量). • 一、中断向量表 • 存放中断服务程序入口地址的表格.结构如图5-15所示。存放在存储器的最低端,占用0~3FFH(1024个)字节的地址空间。

构成:每个中断入口地址占4个字节,低2字节放入口地址的段内偏移量IP,高2字节放段基址CS,4个单元的最低地址称为向量地址(中断向量)。构成:每个中断入口地址占4个字节,低2字节放入口地址的段内偏移量IP,高2字节放段基址CS,4个单元的最低地址称为向量地址(中断向量)。 • 向量地址=中断类型码*4 • 例:设中断类型码13H,放IP=0A00H,CS=1E00H。 • 向量地址=13H*4=4CH,由4CH、4DH单元取出IP值,由4EH、4FH单元取出CS值,得入口地址1EA00H,则从1EA00H处开始执行。 • 可见,计算机通过中断向量转向相应的中断服务程序。

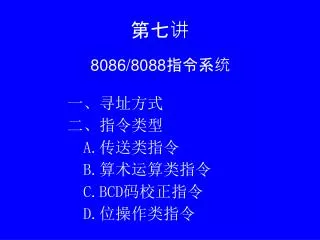

二、中断分类 • 1、内部中断:由软件中断指令INT n 启动,由n提供类型号; • 2、外部中断: • 1)可屏蔽中断INTR——由外部硬设备启动,由硬件提供类型号; • 2)不可屏蔽中断NMI——由CPU内自动提供类型号。

8086/8088的中断源可有256个,如图5-13所示 • 专用5个(内部中断):在某些特定情况下,由CPU内硬件自动提供类型号0~4; • 保留27个(软件中断):由内部软件的中断指令产生,供系统开发用。 • 用户定义224个(外部中断):由外部设备硬件启动。 • 可以利用保留的中断类型码扩充自己需要的中断功能,只要在向量表中加入对应的中断向量即可。

5.3.2 外部中断 • 一、可屏蔽中断INTR 处理过程: • 1)接口发请求,若屏蔽位(可用命令写入)=0, • 通常由可编程中断控制器8259A PIC驱动,INTR=1,一直保持到收到响应信号或撤消请求为止. • 若IF=0(关中断,可由CLI复位),CPU不响应,继续处理下一条指令; • 若IF=1(开中断,可由STI置位),CPU响应, • 2)执行两个INTA总线周期,发两个INTA信号,时序见图5-14, • 第一个INTA信号通知8259A请求已被接收;

在第二个INTA信号有效,8259A送中断类型码(初始化时写入8259A)到数据总线,由CPU启动中断过程,同时撤消中断请求信号.在第二个INTA信号有效,8259A送中断类型码(初始化时写入8259A)到数据总线,由CPU启动中断过程,同时撤消中断请求信号. • 二、不可屏蔽中断NMI • 发生“灾难性”事件(如电源掉电、存储器读写出错、总线奇偶出错或协处理器中断请求等),NMI=1,无法禁止(不受IF影响),优先级比INTR高,且是边沿触发(只要有效宽度大于2T即可),中断类型号为2,CPU响应NMI,不发INTA,不要求外设提供中断向量,自动到08H单元取入口地址。

5.3.3 内部中断 • 通过软件调用的不可屏蔽中断,有以下几种: • 一、溢出中断——类型4(单字节指令) • OF=1,执行INTO,产生一个4类中断。 • 二、除法出错中断——类型0 • 在执行DIV和IDIV后,出现除数为0后商大于寄存器所能表示的范围,CPU产生一个0类中断。 • 三、INT n 指令中断——类型n • 由系统提供或用户定义,CPU执行后,立即产生中断,转向n规定的中断服务程序去,入口地址在初始化时已预置在中断向量表中。

四、断点中断——类型3(单字节指令) • CPU执行INT 3 (简写INT)时,产生中断,进行特殊处理,如显示寄存器、存储单元的内容,以检查程序运行的结果是否正确。在调试时把断点插入程序中的关键之处,命令如-G CS:nnnnH。 • 五、单步(陷阱)中断——类型1 • 当陷阱标志TF=1,8086/8088处于单步工作方式,用-T命令,CPU每执行完一条指令就自动产生一个1型中断,把状态标志PSW、CS、IP压栈,清除TF和IF,则CPU执行单步中断服务程序时以非单步工作方式,单步中断服务程序结束后,

弹出IP、CS、PSW,此时TF=1,CPU返回后以单步方式工作。弹出IP、CS、PSW,此时TF=1,CPU返回后以单步方式工作。 • 单步中断过程可以是:打印或显示寄存器内容、指令指针值或关键的寄存器变量等,详细跟踪一个程序的具体执行过程,确定程序出错的位置。 • TF的设置: 在PSW中,D8=TF • TF置1:PUSHF,将栈顶内容与0100H相“或”,POPF; • TF清0:PUSHF,将栈顶内容与FEFFH相“与”,POPF;

内部中断的特点 • 1、中断类型码或包含在指令中,或是预先规定的; • 2、不执行INTA总线周期; • 3、除单步中断外,任何内部中断都无法屏蔽; • 4、除单步中断外,任何内部中断的优先权都比外部中断的优先权高。8086/8088的中断优先级见表5-1。但执行内部中断时,会响应不可屏蔽中断请求,若用了开中断,也可响应可屏蔽中断请求;

5、若用软件中断INT n 指令,使它与外设的类型码相同,来启动由外设启动的外设中断服务程序,可用于模拟调试外部设备的中断服务程序; • 6、软件中断无随机性; • 7、软件中断可用于管理调用和系统程序的再定位。如:在一个文件中查找一个记录、向另一程序发送一个信息、请求分配存储器空间、互相通信和互相调用。

5.4 I/O接口中的中断控制电路 • 5.4.1 CPU与多个中断源的连接 • 8个外设的中断请求触发器组成一个端口,如图5-16,所有INT信号相“或”后接CPU的INTR端。 • 5.4.2 中断源的识别 • 找到相应的中断服务程序的入口地址。有两种方法: • 1.查询中断 • 收到中断请求,CPU才查询,主要用软件查询。CPU依次读出每一个外设的的外设的中断状态位,通过测试该状态位来判断对应的外设是否发出请求,以转到相应的中断服务程序。

例:4个外设的查询测试程序的流程图和硬件示意图如图5-17,4个请求经“或”输入,若4次都未测到,则由于出错引起,程序转向出错出口。例:4个外设的查询测试程序的流程图和硬件示意图如图5-17,4个请求经“或”输入,若4次都未测到,则由于出错引起,程序转向出错出口。 • 2.向量中断(矢量中断) • 每个外设被指定一个中断向量,当CPU响应时,由硬件的控制逻辑送入中断向量,以提供中断服务程序的入口地址,转入中断服务。 • 4、保护现场(有关寄存器内容和标志寄存器的状态入栈) • 5、执行中断服务程序

6、恢复现场(有关寄存器内容和标志寄存器的状态出栈)6、恢复现场(有关寄存器内容和标志寄存器的状态出栈) • 7、开中断与返回 • 5.4.3 中断优先级 • 根据中断源要求的轻重缓急,排好中断优先次序(即优先级或优先权),先响应优先级最高的中断请求,正在处理中断时,能响应优先级更高的中断请求,而屏蔽同级和较低级的中断请求(即多重中断).

确定中断优先级的方法: • 1.软件查询确定中断优先级 • 硬件:8个外设的中断请求触发器组成一个端口,如图5-18,所有INT信号相“或”后接CPU的INTR端。 • 软件:当CPU响应后,在中断服务程序前加一段判优的查询程序,即CPU逐位检测放在中断寄存器的状态,若有请求,即转入相应的中断服务程序入口。而询问的次序即为优先级的次序。 • 优点:省硬件; • 缺点:中断源较多时,查询花费的时间长,响应慢。

2.硬件查询确定优先级(链式) • 如图5-19,INTR信号的产生同软件查询法,靠近CPU的优先级最高。 • 当INTA=0 • 1)若本级中断触发器=1,EN=1,外设经三态缓冲器往总线送中断标志(类型号),转中断处理;下级门被封锁,INTA不下传。 • 2)若本级中断触发器=0,本级EN=0,不响应,下级门打开,INTA传给下一设备。 • 优点:响应快,硬件较简单。 • 缺点:优先级固定。

三、中断优先级编码电路 • 如图5-20,INT是否传入CPU的INTR端,受三方面控制:1)若中断屏蔽位IMn=0;2)受比较器控制;3)受优先级失效信号( CPU不在处理中断服务时为1)控制。 • 优先级编码器:8个中断输入线,对应产生三位二进制优先编码,最高的为111,最低为000,但只输出优先级最高的一个A到比较器,而优先级寄存器(当前中断服务寄存器)的编码作为另一输入B,1)若AB,“AB”=0,封锁门1,禁止向CPU发INT;2)若“AB”=1,打开门1,INT送入CPU。 • 当CPU响应后,发INTA=0,打开三态缓冲器,中断向量送入CPU.

中断的嵌套 • 中断嵌套(多重中断):当CPU执行优先级较低的中断服务程序时,允许响应优先级更高的中断请求,而挂起正在处理的中断,转去处理较高的中断服务,处理完再返回被中断的较低优先级的中断服务。 • 与单级中断的区别: • (1) 屏蔽本级和较低级中断请求; • (2)为保证中断嵌套,进行中断服务前,在保护现场、屏蔽本级和较低级中断后,要开中 • (3)为使恢复现场不受干扰,先关中断。

5.4.4 中断传送方式的接口电路 • 如图5-21所示中断传送方式的输入接口电路. • 1)输入设备准备好,发选通信号READY,一使数据送入锁存器,二使中断请求触发器U2置1; • 2)若系统允许,中断屏蔽触发器U3已置1,经与门U7向CPU发INTR=1信号; • 3)若开中断(IF=1),则在现行指令执行完后可响应中断,执行中断响应周期; • 4)CPU发INTA=0,一使要求外设接口将中断类型码送上数据总线,二清除中断请求触发器使U2=0; • 5)转去执行中断程序,发IN指令,取数据到数据总线D7~D0 • 6)返回.

5.5 I/O接口芯片概述 • 5.5.1 I/O接口电路的发展与分类 • 1.发展 • 简单接口芯片 • 可编程I/O接口芯片段 • 功能接口板,控制芯片组(芯片组) • 2.分类 • 1)按功能选择的灵活性分 • (1)不可编程接口芯片 • (2)可编程接口芯片

2)按接口的通用性分 • (1)通用接口芯片 • (2)专用接口芯片

5.5.2 简单的I/O接口芯片 • 1.特点与组成 • 电路结构简单,功能单一固定,不可通过指令改变.如: • 1)仅含三态缓冲器的并行接口电路 • Intel 8216, SN74LS244,245等 • 2)仅含数据锁存器的并行接口电路 • 74LS273,375等 • 3)兼具数据锁存器和三态缓冲器的并行接口电路 Intel 8212, 74LS373,375等

2 三种简单的I/O接口芯片 • 在外设接口电路中,对信息进行放大、隔离以及锁存的功能的接口芯片最简单的是缓冲器、数据收发器和锁存器。 • 1)74系列器件 • 是TI公司的中小规模TTL集成电路芯片。从功能和速度分为: • 74nnn——标准TTL • nnn——代表逻辑功能 • 74后跟L——表示低功耗;S——肖特基型 • ALS——高性能; F——高速型

2)锁存器74LS373 • 具有三态总线驱动输出的8D锁存器, 逻辑电路和引脚图如图5-22所示,D触发器时钟连在一起作“锁存允许”(使能)信号G,输出允许为OE-。 • 当G=H,OE=L,Q=D (直通门) • G=L,OE=L,Q=Q0(保持原态) • OE=H,Q=Z (高阻抗) • 用途: • 1、IBM PC/XT机中用于锁存地址信息和页面地址信息

2、匹配外设和微处理器的速度。输入时,锁住设备的输入信息,保持到微处理器取走信息;输出时,锁存微处理器送出的数据直到外设取走数据。2、匹配外设和微处理器的速度。输入时,锁住设备的输入信息,保持到微处理器取走信息;输出时,锁存微处理器送出的数据直到外设取走数据。 • 常用的锁存器还有:74LS273,573,Intel8282和8283等。

3)缓冲器74LS244 • 8缓冲器和线驱动器,逻辑电路和引脚图如图5-23所示,分二路,4根数据线的使能端G连在一起,1A1Y由1G-控制,2A 2Y由2G-控制。 • 当 G=L,Y=A; G=H,Y=Z(高阻态) • 用途: • 1、存储地址驱动器、时钟驱动器和总线定向接收器和定向发送器; • 2、电平转换:CMOS TTL; • 3、IBM PC/XT机中,作存储地址缓冲器/驱动器。 • 常用的缓冲器还有:74LS240和74LS241等。

4)数据收发器74LS245 • 三态输出的8总线收发器,逻辑电路和引脚图如图5-24所示,16个双向传送的数据端, 使能端 G=0,传送 • G=1,隔开 • 方向控制端 DIR=0,B A • DIR=1,A B • 用途: • 用于数据的双向传送、缓冲和驱动。 • 常用的数据收发器还有:74LS243,Intel8286,Intel8287等。

5.5.3 简单的I/O接口芯片的应用举例 • 1.74LS373、245、244在PC/XT机中的应用 • 利用锁存器74LS373和数据收发器74LS245,将8086的双重总线分开。如图15.3和图5-27。

1)地址锁存器74LS373和地址缓冲器74LS244 • AD7~AD0——74LS373的D端——接A7~A0 • A11~A8(不变)——74LS244(驱动器) • A19/S6~A16/S3,A15~A12——74LS373——接系统总线A19~A12 • G(74LS373)——ALE(8288) • OE(74LS373)——AENBRD(DMA应答电路) • 1G(74LS244)

2)双向数据收发器74LS245 • AD7~AD0——74LS245的A • 使局部数据总线和系统总线相连: G(74LS245)——DEN(8288)反相 • DIR(74LS245)——DT/R(8288) • CPU工作时,AENBRD=0,ALE=H, DEN=H, 74LS373、244、245正常工作。 • DMA方式时,74LS373、244、245高阻,与系统总线隔开。

2.用于一般的总线驱动电路 • 在8086系统中,存储器和I/O接口较多,在CPU和系统总线之间要加总线驱动电路。如图5-28所示。 • 要求:CPU能进行常规的存储器读写、I/O读写、中断的响应、总线请求响应以及在RESET有效时的相应操作。

(1)确定器件 • 依提意,双重总线A19/S6~A16/S3,AD15~AD0和BHE/S7共21位用3片74LS373来锁存和驱动,连到系统总线的A19~A0和BHE。而AD15~AD0用二片74LS245驱动,连到系统总线的D15~D0, • 而单向控制信号RD、WR、M/IO、ALE、INTA等用74LS244来驱动。

(2)控制信号的连接 • 两种工作状态: • 1)正常工作状态:CPU进行存储器读写和I/O读写,373、245、244要正常工作,74LS373的OE-、74LS245的G-、74LS244的1G-、2G-都应为L。 • 2)DMA方式和RESET时, 373、245、244输出为高阻状态:74LS373的OE-、74LS245的G-、74LS244的1G-、2G-都应为H。

控制信号的连接 • 因此把74LS373的OE-、74LS245的G-、74LS244的1G-、2G-连一起,由RESET和HLDA经一或门的输出来提供。 • 工作时: • 1)读和中断响应,要求B A即74LS245的DIR=0,可由RD-和INTA-经一与门连到DIR。 • 2)T1时锁存地址,要求74LS373的G=H,可连到ALE。