Efficient Soft Error Verification Methodology for Sequential Circuits Using Probability Transfer Matrices

This paper presents a comprehensive methodology for analyzing soft errors in sequential circuits, emphasizing the development of a novel algorithm for fast reliability evaluation using Probability Transfer Matrices (PTMs). We address the challenges posed by transient errors caused by cosmic rays and high-energy particles, propose a circuit-partitioning based approach, and introduce a heterogeneous PTM construction method. Our experimental results demonstrate significant improvements in scalability and performance, highlighting the effectiveness of our strategy in evaluating circuit vulnerabilities and ensuring robust design.

Efficient Soft Error Verification Methodology for Sequential Circuits Using Probability Transfer Matrices

E N D

Presentation Transcript

SOFT ERROR VERIFICATION FOR SEQUENTIAL CIRCUITS Chien-Chih Yu, Cheng Zhuo Course Advisor: Prof. Valeria Bertacco Dept. of EECS Univ. of Michigan, Ann Arbor

Outline • Motivation • Background • Prior Works • Problem Modeling • Probability Transfer Matrices (PTMs) • Proposed Methodology • Experimental Results • Lessons Learned • Group Dynamic • Conclusion

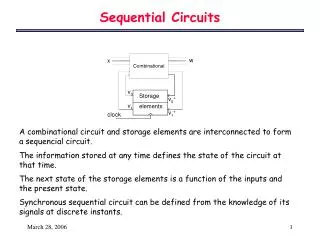

What is Soft Error • Soft errors caused by cosmic rays and high energy particle • Soft errors are transient faults • No standard model for soft errors yet

Nano-scale Transistor Problem • Transistor size becomes smaller than before • Very low supply voltage Source: Intel Crop.

What We Are Working On! CHALLENGES/OPEN ISSUES • Develop a standard model for transient errors • Develop a methodology to estimate the soft errors reliability efficiently and maintain high accuracy • Circuit vulnerability analysis and robust desgin

Our Goal of This Project Your design sequential PTM engine Evaluate the reliability of soft errors Test patterns

PRIOR WORKS • SPICE model-based • Pattern-aware SPICE model evaluation [M. Omana et al., IOLTS, 03] • SEU analysis for cell library characterization [b. Zhang et al., ISQED, 06] • Probability network-based • Bayesian network [T. Rejimon et al., MSCS 05] • Probabilistic transfer matrices (PTMs) [S. Krishnaswamy et al., DATE 05]

Probability Transfer Matrices (PTM) a c b • Source :[S. Krishnaswamy et al., DATE 05] 2 input NAND gate PTM representation a c=0 c=1 a b b 00 01 10 11 c soft error probability P 1-P

Probability Transfer Matrices (contd) Tensor: A = [aij]i,j A B = [aij x B]i,j 23 x 25 25 x 25 25 x 23 23 x 21 ITM Fanout SWAP SWAP • Source: [S. Krishnaswamy et al., DATE 05] (F2F2I)(I SWAP(1,2) NOTpI)(NAND2p NAND2p I)(NAND3p) insert fanout matrices insert additional identical matrices insert swap matrices

Probability Transfer Matrices (contd) 3 inputs Equivalent PTM 23 Apply input probability distribution 21 output = e.g. uniform distribution Prob. Z=0

Drawback of Original PTM Method insert swap matrices levelize that’s why the original method can only handle circuits with <100 gates insert additional ITMs insert fanout matrices Apply tensor operation to every level Apply multiplication to two adjacent levels

CONTRIBUTIONS • FIRST WORK applying the PTM methodology to sequential circuits • Develop a circuit-partition based algorithm for fast soft error reliably evaluation for sequential circuits • Propose heterogeneous PTM construction method • direct constriction • pattern-aware sampling • Extend the scalability of original PTM algorithm

Our Method: Heterogeneous PTM Construction circuit partition

Our Method: Heterogeneous PTM Construction (contd) fanout-free circuit merge two regions re-convergence extraction merge points frontier P Q S R

Our Method: Heterogeneous PTM Construction (contd) fanout-free circuit direct construction No PTM construction here !!! re-convergence circuit Generate PTM from frontier quasi-Monte Carlo sampling

Heterogeneous PTM Construction (contd) • Why our new method has better scalability • Avoid identical matrices insertion • Avoid fanout matrices insertion • Avoid swap matrices insertion • Avoid tensor operation • Reduce #. of multiplication operations • Reduce #. of internal PTMs

Experimental Results (1) Table 1. The Information, Run Time and Memory Consumption for Testcase Circuits

Experimental Results (2) Table 2. Reliability at different cycles for Testcase Circuits

Experimental Results (3) Figure 1. Circuit Reliability w.r.t. Different Gate Error Probability

Lesson Learned • Start early (Of Course) • Divide and Conquer Strategy, for both the project and circuit • Frequent discussion is helpful • Re-convergence region detection is very hard • Maybe more… e.g. coding is bounded whereas debugging is unbounded…

GROUP DYNAMIC Chien-Chih Yu: Top-level proposal, matrix evaluation, PTM modification, circuit partitioning, merge-point detection, program integration, etc. Cheng Zhuo: Top-level proposal, circuit partitioning, pattern-aware sampling, PTM modification, etc.

Conclusion • Develop an algorithm for fast soft error reliability evaluation based on the PTM method • Propose a new PTM generation procedure – Heterogeneous PTM construction method • direct constriction • pattern-aware sampling • Proposed method provides great scalability as well as high performance in both runtime and memory consumption