Sequential Circuits

Sequential Circuits. Lathces & Flip - Flops. A TV channel control example. 0. 1. CH 2. CH 3. 1. 1. 0. CH 1. 0. Outputs. Inputs. Combina t ional Logic. Storage Elements. Next State. State. Introduction to Sequential Circuits. clock. Sequential circuits

Sequential Circuits

E N D

Presentation Transcript

SequentialCircuits Lathces &Flip-Flops

A TV channel controlexample 0 1 CH 2 CH 3 1 1 0 CH 1 0

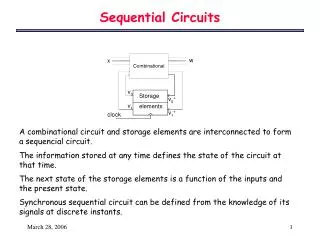

Outputs Inputs Combinational Logic Storage Elements Next State State Introduction to Sequential Circuits clock • Sequential circuits • Combinational logic circuits • State information (stored in memory) • Output is a function of inputs and present state • Can be synchronous or asynchronous

clock period Clocks and synchronization • A clock is a special device that whose output continuously alternates between 0 and 1. • The time it takes the clock to change from 1 to 0 and back to 1 is called the clock period, or clock cycle time. • The clock frequency is the inverse of the clock period. The unit of measurement for frequency is the hertz. • Clocks are often used to synchronize circuits. • They generate a repeating, predictable pattern of 0s and 1s that can trigger certain events in a circuit. • If several circuits share a common clock signal, they can coordinate their actions with respect to one another. • This is similar to how humans use real clocks for synchronization.

0.2ns 0.5ns 0.2 0.4ns 0.5 0.4 0.4 StoringInformation Y S

Race, and Unstable SR Latch S R R SR Q No Change Reset QN Set S Undefined S R Q QN

SR Latch S Q S R QN SR R Undefined Reset Set No Change

No Change No Change Reset Set Undefined SR Latch withControl Input S Q C QN R

D Latch D Q C QN D D C C D with 0 Control D with 1 Control

Q Transparency C • D Latch is called “transparent”: Output follows input instantaneously • Desired behavior: Y changes only once per clock pulse D Q

C D Q Oscillating Unstable LatchTransparency Problem D Q D C 1

S S S Q Q Q C C C R R Q R Q Q S-R Master-Slave Flip-Flop PULSE TRIGGERED Y Glitch 1s Catching Problem S and R must be stableduringclockpulseforthecorrectoperation Master Slave C S R Y Q

D D S Q Q Q C C C Q R Q Q Negative Edge Triggered D Flip-Flop C D Q1 Q2

D D S Q Q Q C C C Q R Q Q PositiveEdge Triggered D Flip-Flop C D Q1 Q2

S S D D C C R R C C Triggered D Triggered SR Triggered SR (b) Master-Slave Flip-Flops D D C C Triggered D Triggered D (c) Edge-Triggered Flip-Flops Standard Symbols for Flip-Flops • PulseTriggered • Edge-Triggered: Triggered D

S D Q C Q R Direct Inputs • Direct R and/or S inputs that control the state of the latches within the flip-flops asynchroniously. • For the example flip-flop shown • 0 applied to R resets the flip-flop to the 0 state • 0 applied to S sets the flip-flop to the 1 state

Q(t) Q(t+ 1) S R Operation 0 0 0 X No change 0 1 1 0 Set 1 0 0 1 Reset 1 1 X 0 No change S-R Flip-Flop Descriptors S R Q(t + 1) Operation 0 0 Q ( t ) No change 0 1 0 Reset 1 0 1 Set 1 1 ? Undefined • Characteristic Table • ExcitationTable • Characteristic Equation

D Q(t 1) Operation + 0 0 Reset 1 1 Set Operation Q(t +1) D 0 0 Reset 1 1 Set DFlip-Flop Descriptors • Characteristic Table • ExcitationTable • Characteristic Equation

J C J K Q(t + 1) Operation K 0 0 Q ( t ) No change 0 1 0 Reset 1 0 1 Set 1 1 Complement Q ( t ) D J K C J-K Flip-flop + 1) Q(t) Q(t J K Operation 0 0 0 X No change 0 1 1 X Set 1 0 X 1 Reset 1 1 X 0 No Change • Characteristic Table • ExcitationTable • Characteristic Equation

T C D T C TFlip-flop + + Q(t 1) T Operation T Q(t 1) Operation Q ( t ) 0 No change 0 Q ( t ) No change Q ( t ) 1 Complement 1 Q ( t ) Complement • Characteristic Table • ExcitationTable • Characteristic Equation

D T C C Flip-flop Behavior Example • Use the characteristic tables to find the output waveforms for the flip-flops shown: Clock D,T QD QT

S C R J C K Flip-Flop Behavior Example (continued) • Use the characteristic tables to find the output waveforms for the flip-flops shown: Clock S,J R,K QSR ? QJK