Understanding Sequential Circuits and D Flip-Flops in VHDL

This document introduces sequential circuits, highlighting their reliance on both current and past inputs. It explains the role of memory elements, particularly flip-flops, as the fundamental building blocks for storing information in these circuits. A D flip-flop, which retains its value with each clock cycle, is discussed in detail, including its state diagram and functionality. Additionally, an overview of T flip-flops is provided, explaining how they toggle states based on a control signal. The assessment methods reflect a balanced approach to evaluating both group and individual learning in this context.

Understanding Sequential Circuits and D Flip-Flops in VHDL

E N D

Presentation Transcript

SequentialCircuits (Introduction)

Index IIntroduction II D flipflop IIIVHDL for a D flipflop IVT flipflop

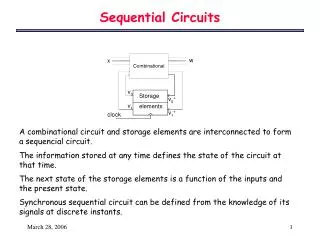

I. Introduction Asequentialcircuitisdependentonboththecurrent and thepast inputs of thesystem . In ordertorememberthehistory of the inputs, sequentialcircuitsmusthavememoryelements. Flip-flopsare thebasicmemoryelementsforstoringinformation. They are the fundamental building blocks of sequentialcircuits. A single flipflop can storeonlyone bit of information. In ordertosynchronizeallstatechangesitisrequired a clocksignal

II. D Flip-flop Whentheclockiseither 0 or 1, theflipflopretainsitscurrentvalue Thesmalltriangleindicatesthattheflip-flopistriggeredbytherisingedge of theclock

II. D Flip-flop StateDiagram Itportraysgraphicallytheoperation of theflip-flop

IV. T Flip-flop When T isasserted (T = 1) theflipfloptoggles at each active edge of theclock and when T is de-asserted , theflipflopkeepsitscurrentstate.

Continuousassessment Assessment takes into account: group work and individual learning - Problem-solving exercises 30 % - Group e-Portfolio 15 % - Applied project 20 % - Basic knowledge tests 25 % - Attitude and participation 10 % Group work Individual work