Latest Developments in Vertex Detector Column Parallel CCDs for ILC

130 likes | 258 Views

This presentation highlights the latest advancements in the Vertex Detector leveraging Column Parallel CCD technology. Featuring five layers, each with minimal material usage (~0.1% X0) and high-resolution pixels (20μm x 20μm), the design accommodates 800 million channels. Background rates dictate separate readouts for each column, with innovative readout ASICs integrating amplifiers, ADC, and digital processing. Prototypes demonstrate reduced noise and robust performance, paving the way for efficient data acquisition and processing, crucial for the International Linear Collider (ILC) experiments.

Latest Developments in Vertex Detector Column Parallel CCDs for ILC

E N D

Presentation Transcript

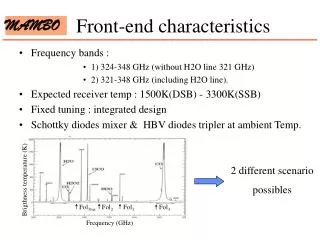

LCWS 2005 Stanford Joel Goldstein, RAL for the LCFI Collaboration Latest Developments from the CCD Front End

Reminder: ILC Vertex Detector Column Parallel CCDs Conceptual Readout Scheme First Generation Prototypes Second Generation Prototypes Outline

The Vertex Detector • 5 layers (15-60mm) • ~ 0.1% X0 per layer • 20 m 20 m pixels • 800 million channels • Background rates force readout • 50 s for Layer 1 • 250 s for Layer 2

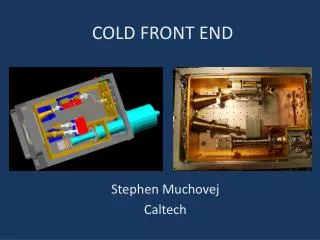

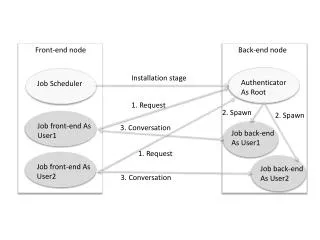

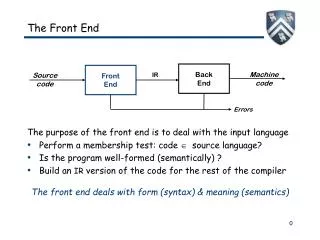

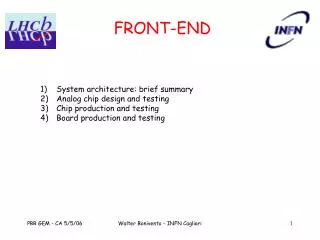

Separate readout for each column Readout ASIC bump-bonded to CCD ASICs contain amplifiers, ADC and digital processing N+1 Column Parallel CCD Readout time = (N+1)/Fout Column Parallel CCDs

Layer 1 read out 20 times per bunch train 50k z pixels Layers 2-5 read out 5 times per bunch train 31k z pixels 4.4 GPixels in total Have to sparsify at front end Ladder Readout

Amplification ADC Detector Level DAQ Filtering Clustering Multiplexer

Front End Readout Chain 1.3 million hits = 20 Mbytes per bunch train

First Prototype CPC/CPR • Column parallel CCD principle • proven • Noise < 100 electrons • Minimum clock ~1.9 V Voltage Amplifiers (non-inverting) 6 keV X-rays • No sparsification in ASIC Charge Amplifiers (inverting)

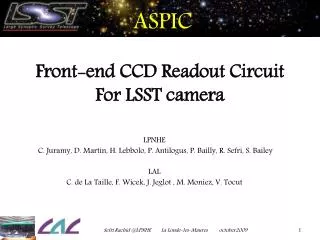

No major changes to amplifiers or ADC Digital cluster finding: 2x2 kernel Extended cluster read out 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 5 5 0 0 0 0 0 5 5 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Cluster found Expanded cluster to be read out Next Generation ASIC

CPR-2 DATA Output Sparsification Cluster Binary 5-bit ADC Preamp Input & Multiplexing Finding Conversion

IBM 0.25 m 6 x 9.5 mm Chips have arrived at RAL Stand alone testing starting Test features: direct analogue I/O pads I/O serial register between ADCs and cluster logic CPR-2

First generation CPCCD/ASIC tested Second generation ASIC ready for testing Cluster finding implemented Sparsification at front end Major steps on road to ILC readout Summary