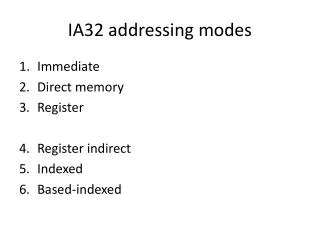

CPU08 ADDRESSING MODES

CPU08 ADDRESSING MODES. ADDRESSING MODES. Inherent Immediate Direct Extended Indexed Relative Memory to Memory. Memory. CPU. program space. A. X X. 4 F. ocl*. X X. ocl + 1. 0 0. data space. X X. X X. Inherent Addressing. Has no operand

CPU08 ADDRESSING MODES

E N D

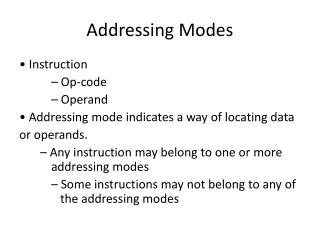

Presentation Transcript

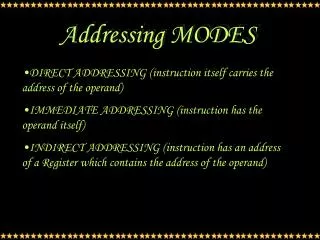

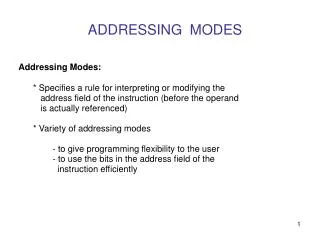

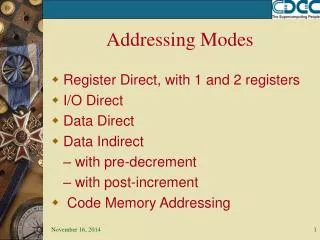

ADDRESSING MODES • Inherent • Immediate • Direct • Extended • Indexed • Relative • Memory to Memory

Memory CPU program space A X X 4 F ocl* X X ocl + 1 0 0 data space X X X X Inherent Addressing • Has no operand • Operates mostly on CPU registers or bits • Example: CLRA * opcode location

Memory CPU program space A A 6 ocl X X F F ocl + 1 F F data space X X X X Immediate Addressing • Specifies value directly, not an address of the value • Indicated by # • Has one operand • Contained in the byte or bytes immediately following opcode • Example: LDA #$FF

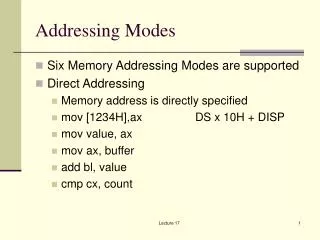

Memory CPU program space A B 6 ocl X X 5 0 ocl + 1 A A data space A A 0050 X X 0051 Direct Addressing • Specifies 8 bit address of operand • Upper byte of 16 bit address is assumed to be $00 • Used to access first 256 bytes of memory • Address contained in the byte immediately following opcode • Example: LDA $50

Memory CPU program space A C 6 ocl X X 0 4 ocl + 1 0 0 ocl + 2 A A data space A A 0400 X X 0401 Extended Addressing • Specifies 16 bit address of operand • Used to access address greater $00FF memory • Address contained in the two bytes immediately following opcode • Example: LDA $0400

Memory program space CPU 7 F ocl X X ocl + 1 H:X X X ocl + 2 04 00 data space X X 0400 0 0 0400 Indexed Addressing- NO Offset - • Specifies H:X index register contains the address of the operand • Example: CLR ,X

Memory program space CPU 6 F ocl 0 A ocl + 1 H:X X X ocl + 2 04 00 data space X X 040A 0 0 040A Indexed Addressing- 8 Bit Offset- • Unsigned 8 bit offset + unsigned H:X register = memory location • H:X register is unaffected • 8 bit offset is the byte immediately following opcode • Example: CLR 10,X

Memory program space CPU D 7 ocl A 0 1 ocl + 1 55 0 0 ocl + 2 H:X data space 00 50 X X 0150 5 5 0150 Indexed Addressing- 16 Bit Offset - • Unsigned 16 bit offset + unsigned H:X register = memory location • H:X register is unaffected • 16 bit offset is the two bytes immediately following opcode • Example: STA $0100,X

Table 0100 element 1 element 2 element 3 • • • • H:X=N element n element n+1 element n+2 element n+3 Indexed Addressing- 8 & 16 Bit Offsets - • Commonly used to access elements of data structures • Offset would be base address of structure • Index register would contain displacement to the Nth element ORG $100 Table FCB $10, $20, $30, $40 ....... • • * Calculate displacement for element N in A • CLRH TAX LDA Table,X NOTE: If Table were in the first 256 bytes of memory, most assemblers would use an 8-bit offset instruction element 1

Memory program space CPU 9 E ocl A E 7 ocl + 1 FF 0 5 ocl + 2 SP stack space 00 D0 X X 00D0 • • • F F 00D5 Indexed Addressing- Using Stack pointer and 8-Bit Offset - • Unsigned 8 bit offset + unsigned SP register = memory location • SP register is unaffected • 8 bit offset is the byte immediately following opcode bytes • Example: STA 5,SP

CPU Memory program space A FF 9 E ocl D 7 ocl + 1 SP 0 1 ocl + 2 00 D0 0 0 ocl + 3 data space X X 00D0 • • • F F 01D0 Indexed Addressing- Using Stack pointer and 16-Bit Offset - • Unsigned 16 bit offset + unsigned SP register = memory location • SP register is unaffected • 16 bit offset is the two bytes immediately following opcode bytes • Example: STA $100,SP • NOTE: If interrupts are disabled, SP can be used as an additional index register • Less efficient because of pre byte

00C0 X X SP temp 1 temp 2 msb temp 2 lsb param 3 param 2 param 1 Stack Pointer- 8 Bit Offsets - • High level language support • Compilers often place parameters for procedures and temporary storage on the stack • Stack Pointer addressing is an efficient means to access this information • temp 1 = 1,SP • temp 2 = 2,SP and 3,SP • param 3 = 4,SP • param 2 = 5,SP • param 1 = 6,SP • What happens if the stack pointer moves? • ie: more information is pushed onto the stack. • Where is -1,SP ?

Relative Addressing Cont. • Used in all conditional branch instructions • If condition is TRUE Program Counter = Program Counter + Signed 8 bit offset • else Program Counter is unaffected • Example: BEQ $8100 CPU Memory PC program space 81 52 2 7 $8150 A E $8151 if condition true X X $8152 81 00

Memory program space CPU H:X 7 1 ocl 04 00 0 2 ocl + 1 X X ocl + 2 A 04 01 55 data space 04 02 X X 0400 • • • 5 5 04 11 0410 Indexed Addressing- No Offset with Post Increment - • Specifies H:X index register contains the address of the operand • After address of operand is calculated, H:X is incremented by 1 • Example: Loop CBEQ X+,Out BRA Loop Out . . . .

Memory program space CPU H:X 7 1 ocl 04 00 5 0 ocl + 1 0 2 ocl + 2 A 04 01 55 data space 04 02 X X 0450 • • • 5 5 04 11 0460 Indexed Addressing- 8 bit Offset with Post Increment - • Just like indexed addressing with 8 bit offset, plus post increment • After address of operand is calculated, H:X is incremented by 1 • Example: Loop CBEQ $50,X+,Out BRA Loop Out . . . .

Memory to Memory Addressing • Used to move information from one location to another • Does not use/affect CPU registers • Except when using indexed addressing with post increment • More efficient than Load/Store combination • Can only be used with the MOV instruction • MOV Source Address,Destination Address • Four variations: • Immediate to Direct • Direct to Direct • Indexed to Direct with Post Increment • Direct to Indexed with Post Increment

program space data space X X 6 E ocl 00F0 A A ocl + 1 F 0 ocl + 2 A A 00F0 Memory to Memory Addressing - Immediate to Direct - • Source is one byte immediate value • Destination must be in first 256 bytes of memory • Example usage: • Initialization of variables or registers MOV #$AA,$F0 Memory

program space data space data space X X 4 E ocl 00F0 0 0 ocl + 1 5 5 0000 F 0 ocl + 2 5 5 00F0 Memory to Memory Addressing - Direct to Direct - • Source must be in first 256 bytes of memory • Destination must be in first 256 bytes of memory • Example usage: • Moving data from one page zero location to another MOV $00,$F0 Memory

Memory program space CPU 7 E ocl 1 8 ocl + 1 H:X 04 00 X X ocl + 2 data space data space X X 0018 5 0 0400 04 01 5 0 0018 Memory to Memory Addressing - Indexed with Post Increment to Direct - • Source may be any where in memory map • Destination must be in first 256 byte of memory • Example usage: • Writing data to a communications device from a buffer MOV X+,$18

Memory program space CPU 5 E ocl 1 8 ocl + 1 H:X 04 00 X X ocl + 2 data space X X data space 0400 5 0 0018 04 01 5 0 0400 Memory to Memory Addressing - Direct to Indexed with Post Increment - • Source must be in first 256 byte of memory • Destination may be any where in memory map • Example usage: • Writing data from a communications device to a buffer MOV $18,X+

0100 RCVPTR • • • XMTPTR 010A MEMORY TO MEMORY- EXAMPLE - ORG $50 RCVPTR RMB 2 XMTPTR RMB 2 ORG $100 RCVB RMB 10 XMTB RMB 10 Receive • • • LDHX RCVPTR • • • MOV $18,X+ • • • STHX RCVPTR • • • Transmit • • • LDHX XMTPTR • • • MOV X+,$18 • • • STHX XMTPTR • • • • SCI communication handling routines

Addressing Modes Summary • MODE Example Usage • Inherent PULX • Immediate ADD #$10 • Direct SUB $50 • Extended SUB $200 • Indexed • no offset STA ,X • 8 or 16 bit offset LDX $200,X • post increment CBEQ X+,There • 8 bit offset w/ post inc CBEQ $50,X+,There • Stack Pointer • 8 or 16 bit offset CLR 5,SP • Relative (PC) BEQ Here • Memory to Memory • Immediate to Direct MOV #$00,$A0 • Direct to Direct MOV $18,$F0 • Indexed post inc to Direct MOV X+,$12 • Direct to Indexed post inc MOV $12,X+

C1. value 55. X register. address $220. branch opcode. bytes forward or Direct requires a to whose value is from 3. Load the X register with the 2. Load the X register with the an offset. The register value is a 4. Load accumulator A with the register higher than the memory contents of the memory location contents of the memory location contents of memory location hex whose address is the contents of X whose address is the contents of the 1. Load accumulator A with the hex (constant/variable). 7. Direct and Extended address modes generate a to ; Extended requires a (offset, X register) as the distance to select the item to be accessed. 8. A common way to use the 16-bit offset with index address mode is to use the LDA LDX LDX For each operation, complete the instruction using the appropriate addressing mode. Also indicate the length (# of bytes) of the instruction and execution time (# of cycles). 5. Normal branch instructions can change the program counter to an address as far as Address Modes Exercises . LDA (offset, X register) as the starting address to a table of items and the 6. Indexed addressing generates a memory address that is the sum of two values: a register and bytes backward in program memory relative to the address of the (one/two) byte address in program memory whose value is from Instruction: Operand: Bytes: Cycles: (constant/variable) and the offset value is a (one/two) byte address in program memory (constant/variable) address. HC08-addrSol