Addressing Modes

Addressing Modes. Register Direct, with 1 and 2 registers I/O Direct Data Direct Data Indirect – with pre-decrement – with post-increment Code Memory Addressing. Register Direct #1 REG. Register Direct #2 REGS. I/O Direct. Data Direct. Data Indirect. clr r27 ; Clear X high byte

Addressing Modes

E N D

Presentation Transcript

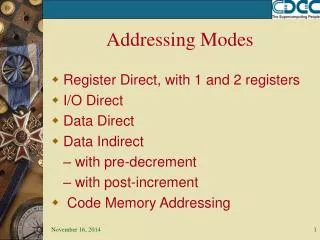

Addressing Modes • Register Direct, with 1 and 2 registers • I/O Direct • Data Direct • Data Indirect – with pre-decrement – with post-increment • Code Memory Addressing

clr r27 ; Clear X high byte ldi r26,$60 ; Set X low byte to $60 st X+,r0 ; Store r0 in data space loc. $60(X post inc) st X,r1 ; Store r1 in data space loc. $61 ldi r26,$63 ; Set X low byte to $63 st X,r2 ; Store r2 in data space loc. $63 st -X,r3 ; Store r3 in data space loc. $62(X pre dec)

Loads one byte pointed to by the Z-register into the destination register Rd. This instruction features a 100% space effective constant initialization or constant data fetch. Not all variants of the LPM instruction are available in all devices.

Constant byte address is specified by the Z-register contents. The 15 MSBs select word address. For LPM, the LSB selects low byte if cleared (LSB = 0) or high byte if set (LSB = 1).

I/O Register $3F : SREG • All Bits are R/W: –I – Global Interrupt Enable –T – Bit Copy Storage –H – Half Carry Flag –S – Sign Bit –V – Two’s Complement Overflow Flag –N – Negative Flag –Z – Zero Flag –C – Carry Flag

Instruction Examples: Add • Math – Add ADD Rd, Rr– Adds two registers – Rd <- Rd + Rr ADC Rd, Rr– Add with Carry two registers – Rd <- Rd + Rr + C ADIW Rdl, K– Add Immediate to Word – Rdh:Rdl <- Rdh:Rdl + K

Other Math and Logic • Subtract • Logical AND • Logical OR • Exclusive OR • One’s Complement , COM Rd • Two’s Complement, NEG Rd • Increment/Decrement, INC Rd, DEC Rd • Set Registers and Bits in Registers, SBR Rdx,k SER Rd ***SBI **

Branch Instructions • RJMP/RCALL – Relative Jmp (+/-k) 2k RJMP OK NOT_OK: ADD R1,R5 OK: INC R1

cpi r16,$42 ; Compare r16 to $42 brne error ; Branch if r16 <> $42 rjmp ok ; Unconditional branch error: add r16,r17 ; Add r17 to r16 inc r16 ; Increment r16 ok: nop ; Destination for rjmp (do nothing)

CONTD… • IJMP/ICALL – Indirect Jmp (Z Reg) LDI R30,add_low LDI R31,add_high IJMP • RET/RETI – Return from Call/Interrupt • CP* - Compare CP R18,R19

CONTD… • SB* - Skip if Bit in Register or I/O is set/clr BACK: IN R3,PINB SBRC R3,0 RJMP BACK IN R4,PIND • BR* - Branch if blahhhh.

Data Transfer Instructions • MOV – Move between register MOV R16,R17 • LD/LDI – Load / Load Immediate LD R15,X+ LD R15,-X • ST////STI – Store / Store Immediate • IN/OUT – In and Out Ports IN R1,PINB OUT PORTC,R1

CONTD.. • PUSH/POP – On and off stack PUSH R1 POP R1

Bit and Bit Test Instructions • SBI/CBI – Set / Clear Bit in register SBI A,s CBI A,s • LSL/LSR – Logical Shift Left/Right LSR R16 • ROL/ROR – Rotate Left/Right (thru C) ROL R16

Bit and Bit Test Instructions • BST RS,s bit store bit s of Rs in t flag • BLD RS,s bit load t flag in bit s of Rs