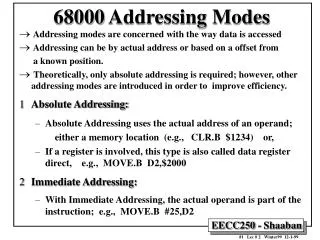

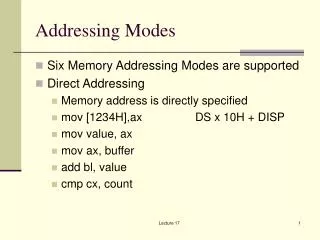

Addressing Modes

Addressing Modes. Addressing Modes. Implicit part of CPU12 instructions 16-bit effective address Each addressing mode except inherent mode generates a which is used during the memory reference portion of the instruction. Effective address computations do not require extra execution cycles.

Addressing Modes

E N D

Presentation Transcript

Addressing Modes • Implicit part of CPU12 instructions • 16-bit effective address • Each addressing mode except inherent mode generates a which is used during the memory reference portion of the instruction. • Effective address computations do not require extra execution cycles.

Addressing Modes • Inherent (INH) • Immediate (IMM) • Direct (DIR) • Extended (EXT) • Relative (REL) • Indexed (IDX,IDX1,IDX2) • Indexed-indirect ([D,IDX],[IDX2])

Inherent Addressing ModeINH • Either, the instruction has no operand • Ex: NOP A7 O • Or, all operands are in internal CPU registers • Ex: INX 08 O (operand is X register)

Immediate Addressing ModeIMM • Operands are included in the instruction stream and are fetched into the instruction queue one 16-bit word at a time during normal program fetch cycles. • LDAA #$55 86 55 P • LDAA #55 86 37 P • LDX #$1234 CE 12 34 PO • LDY #$67 CD 00 67 PO

Direct Addressing ModeDIR • Also known as zero-page addressing as it is used to access operands in the address range $0000-$00FF. • LDAA $55 96 55 rPf • LDY $67 DD 67 RPf

Extended Addressing ModeEXT • The full 16-bit address of the memory location to be operated on is provided in the instruction. • LDAA $F03B B6 F0 3B rPO • LDY $6776 FD 67 76 RPO

Relative Addressing ModeREL • Relative to PC. • Used only by branch instructions. • If the offset is 0, the CPU executes the instruction immediately following the branch instruction, regardless of the test involved.

Relative Addressing ModeREL • Short branch instructions consist of an 8-bit opcode and a signed 8-bit offset contained in the byte that follows the opcode • The numeric range of offset values is [$80,$7F], i.e. [–128,127]. • BCC L1 24 34 PPP/P L1 is a label in [PC-128,PC+127] range.

Relative Addressing ModeREL • Long branch instructions consist of an 8-bit prebyte, an 8-bit opcode, and a signed 16-bit offset contained in the two bytes that follow the opcode. • The numeric range of offset values is [$8000,$7FFF], i.e. [–32768,32767]. • LBCC L1 18 24 25 55 OPPP/OPO L1 is a label in [PC–32768,PC+32767] range.

Relative Addressing ModeREL • Loop primitive instructions consist of an 8-bit opcode, an accumulator or a register and a signed 9-bit offset. • The numeric range of offset values is [$100, $0FF], i.e. [–256,255] • DBEQ B, L1 04 01 25 PPP/PPO L1 is a label in [PC,PC+255] range • DBEQ B, L1 04 11 05 PPP/PPO L1 is a label in [PC-256,PC) range

Relative Addressing ModeREL • Bit-condition branches test whether bits in a memory byte are in a specific state. • The numeric range of offset values is [$80, $7F], i.e. [–128,127] • BRCLR $35,#$25,L1 4F 35 25 21 rPPP L1 is a label in [PC-128,PC+127] range

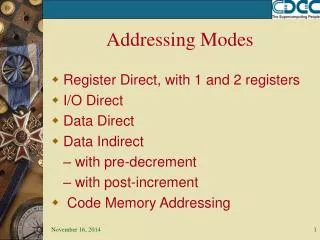

Indexed Addressing ModeIDX, IDX1, IDX2 • Offset is added to the base index register (X, Y, SP, or PC) to form the effective address of the memory location that will be affected by the instruction. • A postbyte is used to do the following tasks: • Specify which index register is used • Determine whether a value in an accumulator (A, B, or D) is used as an offset • Enable automatic pre- or post-increment or pre- or • post-decrement • Specify size of increment or decrement • Specify use of 5-, 9-, or 16-bit signed offsets • Automatic pre- or post-increment or pre- or post-decrement by –8 to +8

5-bit Constant Offset Indexed AddressingIDX • The numeric range is [–16,+15] • Syntax: <opcode> xb • xb=rr0nnnnn rr=00 for X, 01 for Y, 10 for SP, 11 for PC • Assume (X)=$1000, (Y)=$2000 LDAA 0,X A6 00 rPf STAB –8,Y 6B 58 Pw After execution: • (X)=$1000, $1000=X → (A) • (Y)=$2000, (B) → Y-8=$1FF8

9-bit Constant Offset Indexed AddressingIDX1 • The numeric range is [–256,+255] • Syntax: <opcode> xb ff • xb=111rr00s ff: offset without sign bit. • Assume (X)=$1000, (Y)=$2000 LDAA $FF,X A6 E0 FF rPO STAB –20,Y 6B E9 EC PwO After execution: • (X)=$1000, $10FF=X+$FF → (A) • (Y)=$2000, (B) → Y-$14=$1FEC

16-bit Constant Offset Indexed AddressingIDX2 • Whole 64Kbyte address space • Syntax: <opcode> xb ee ff • xb=111rr010 ee ff: offset • Assume (X)=$1000 LDAA $FFFF,X A6 E2 FF FF frPP After execution: • (X)=$1000, $0FFF=X+$FFFF → (A)

Auto Pre/Post Decrement /Increment Indexed AddressingIDX • The index register can be incremented or decremented by an integer value either before or after indexing takes place. • incremented by any integer value [ 1,8], i.e. [0000,0111] • decremented by any integer value [–8 , –1], i.e. [1000,1111] • Syntax: <opcode> xb • xb=rr1pnnnn p:0 (pre) Assume (X)=$1000 LDAA 3,X+ A6 32 rPf After execution: $1000→ (A), (X)=$1003

Accumulator Offset Indexed AddressingIDX • The offset is in one of the accumulators (A, B, or D). • Syntax: <opcode> xb • xb=111rr1aa aa:00 for A, 01 for B, 10 for D. Assume (X)=$1000 LDAA B,X A6 E5 rPf After execution: (X)=$1000, $1000+(B)→ (A),

Indexed-Indirect Addressing Modes[D,IDX],[IDX2] • Each index register is assumed to be a pointer to a table of pointers or addresses • 16-bit offsets.

16-bit Constant Offset Indexed Indirect Addressing[IDX2] • Whole 64Kbyte address space • Syntax: <opcode> xb ee ff • xb=111rr011 ee ff: offset • Assume (X)=$1000 (the base address of a table of pointers). • Assume X+10:X+11= $2000 • LDAA [10,X] A6 E3 00 10 fIPrPf • Execution • Add the value 10 to the value in X to form the address $100A. • Fetch an address pointer ($2000) from memory at $100A. • Read the value in $2000 is read and load into A • After execution: • (X)=$1000, ($100A:$100B)=$2000 → (A)

Accumulator D Indirect Indexed Addressing[D, IDX] • The offset is in one of the accumulators (A, B, or D). • Syntax: <opcode> xb • xb=111rr011 Assume (X)=$1000 and D=0002 and $1002:$1003=$1015 and $1015=$25 LDAA [D,X] A6 E3 fIfrPf • Execution • Add D (i.e. 2) to the value in X to form the address $1002. • Fetch an address pointer ($1015) from memory at $1002. • Read the value in $1015 and load into A • After execution: • (X)=$1000, ($1000+D)=$1015 → (A)