VLSI áramkörök

2.75k likes | 2.89k Views

VLSI áramkörök. Történelem Planar techn. Dinamikus – kapacitív tárolás Küszöbfeszültség instabilitás – analóg… CODEC – telefónia EPROM – floating gate Mikroprocesszor, memóriák Gordon Moore Scale-down Áramkör-elmélet (kódolás, szűrés, etc.) Analogic „electronic grade”

VLSI áramkörök

E N D

Presentation Transcript

VLSI áramkörök VLSI

Történelem • Planar techn. • Dinamikus – kapacitív tárolás • Küszöbfeszültség instabilitás – analóg… • CODEC – telefónia • EPROM – floating gate • Mikroprocesszor, memóriák • Gordon Moore • Scale-down • Áramkör-elmélet (kódolás, szűrés, etc.) • Analogic • „electronic grade” • Team – tudományágak • „Intellectual property”, IP VLSI

1. Alapfogalmak VLSI

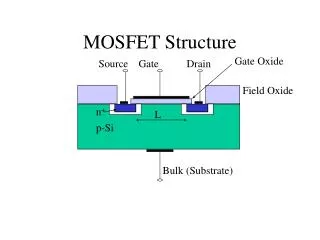

gate-oxid polysilicon gate Gate Drain Source csatorna n+ n+ p-szubsztrát Rövidcsatornás „telítéses” üzem: Küszöbfeszültség alatti működés: VLSI

Drain Cdb Cgd Szubsztrát Gate Cgs Csb Cgb Source Parazita elemek VLSI

Gate oxid réteg UG poliszilicium gate réteg US UD n-adalékolt drain réteg Nincs parazita Csatorna a p-szubsztrátban Szigetelt hordozó pl. zafír Gate-oxid réteg UG1 1. poliszilicium gate réteg US UD n-adalékolt source réteg n-adalékolt drain réteg 2. poliszilicium gate réteg Csatorna a p-szubsztrátban Szilicium hordozó réteg SOI-áramkörök n-adalékolt source réteg Kettős-gate struktúra. VLSI

T2 B T1 Cp A • Szubsztrát visszahatás Usb ΔVth=0,5 Usb 1/2 VLSI

nMOS-tranzisztor pMOS-tranzisztor G G S D S D n-zseb p+ n+ p-szubsztrát Latch-up • Latch-up VLSI

MOS tranzisztor helyettesítőképe Gate rg Ugs’ Cgs Cgd ri gmUgs’ rs rd Source Drain Cgb Cdb Idb Csb D1 D2 Bulk (szubsztrát) VLSI

Szubsztrát Gate Drain Source n+ p n+ Hordozó p L • Vertikális tranzisztor VLSI

Bázis Kollektor Emitter n+-emitter n+-kollektor hozzávezetés p-bázis n-kollektor n+-kollektor eltemetett réteg p-szubsztrát • Integrált bipoláris tranzisztor VLSI

3. VLSI chip 2. VLSI chip Tokozás 1. VLSI chip Kerámia hordozó Tokozások MCM, szendvics-szerkezet (mikrohullámú összeköttetések) VLSI

Logikai családok 1.statikus CMOS 2. dinamikus CMOS (Domino) 3. többkimenetű dinamikus CMOS 4. transzfer gates 5. áramkapcsolt (CML) 6. kaszkád feszültség-kapcsolt (CVSL) 7. emittercsatolt (ECL) 8. BiCMOS 9. adiabatikus, retractile VLSI

Vcc p p A Y=A +B B C t n n 1. Statikus CMOS logika. VLSI

2. Dinamikus CMOS logika. Vcc ELŐTÖLTÉS p Y=A.B n A C ki B n n KIÉRTÉKELÉS VLSI

VCC 3. Több-kimenetű dinamikus CMOS logika. T1 Y1 C1 D T2 Y2 C2 A E M F B VLSI

4. Transzfer-gates logika. p A n A Y=A B p B n VLSI

5. Current Mode Logic, CML VDD R1 A·B+C·D URef URef D B A C VLSI

Q Q VDD T4 T3 Q T1 A A T2 6. Kaszkád feszültségkapcsolt logika (Cascade Voltage Switch Logic, CVSL) Ellentétes (differenciális)vezérlés Ha bemeneteklebegnek, akkor kapacitív tárolás VDD T4 T3 Q T1 T2 D D CLK VLSI

7. Emittercsatolt (ECL) logika. Vcc R1 R2 B A Uref Y=A . B VLSI

Vcc T1 p A Q1 n T2 A T3 Ct n Q2 n T4 8. BiCMOS logika VLSI

GHz-es CMOS logikák speciális problémái időzítés – fázisjelek deskew áramkörök jel-regenerálás, átmeneti tárolók (transzparens latch-ek) differenciális jel-vezetés VLSI

Logikai alap-áramkörök a) alapkapcsolások (inverterek, utánhúzó inverter, Schmitt-trigger) b) statikus kombinációs áramkörök (Hidkapcsolás, TG összeadó, RS-ff,) c) statikus tárolók (kapuzott D-ff, embedded, Shift-reg., SH-reg telep nélkül,) d) dinamikus CMOS áramkörök (2-fázisú tároló, Domino, alternate, C2MOS latch, pipeline, késleltetések, multiple Domino, barrel shifter, 4-fázisú logika, VLSI

Vcc T3 VGG n T1 n Cf A Cp Ct n A T2 Vcc p A A n Ct CMOS alapinverter Utánhúzó inverter VLSI

C1tároló Schmitt-trigger Vcc Vcc Ube T1 T4 p p Uki Ube glitch n C2 n T5 T2 t T6 n n Vcc T3 pMOS duális hálózat A A B B B B Hídkapcsolások. C C C C D D VLSI

VCC p Q Q n C2 C1 n n SET RESET T1 Q p n Statikus RS-tároló. VCC p p T4 T5 Q T2 T3 D D Kapuzott statikus RS-tároló. T1 CLK VLSI

VCC p Q Q n C2 C1 n n SET RESET T1 p n Statikus RS-tároló. Brute force!!! VLSI

Vcc Master-Slave dinamikus T-tároló p p Q Q n n n n CLK CLK n n CLK C2 C1 n n Beágyazott kvázi-statikus D-tároló. Kvázi-statikus D-tároló. Vcc Vcc Vcc p tartás p p beírás Vcc D p Q p p beírás n Q Vcc D n n n p C1 n n beírás tartás tartás n VLSI

Vcc DOMINO CMOS dinamikus, egyfázisú logika p Y=A.B A n C ki Cparazita B n Vcc Vcc Vcc n nMOS logika A.B A.B Y=A.B.D C3 C1 A C2 B D Statikus inverter DOMINO CMOS fokozatok összekapcsolása statikus inverterrel VLSI

C2MOS latch Vcc p p Uki Ube n Ctároló n Alternáló fokozatok alkalmazása Vcc Vcc p p pMOS logika n A p C1 B p n D Y=A . B . D n n Cki nMOS logika VLSI

Vcc Vcc Vcc Vcc Vcc p p p p p A n nMOS logika nMOS logika pMOS logika pMOS logika C1 C1 B Uki n Ctárolót’rol= n n n n C2 n C2 “ -szekció “ C2MOS latch VLSI

VDD VDD T4 T7 CLK Q I1 I2 I3 Q M CLK C2 C1 T3 T6 T2 D T5 CLK T1 CLK Gyors beírású, a kimeneten megfogott D-tároló VLSI

- szekció Pipeline Domino CMOS logika. - szekció - szekció Kiértékelés Előtöltés Előtöltés 0 1 1 0 Kiértékelés Előtöltés Kiértékelés VLSI

T1 Y1 C1 T2 D Y2 C2 A E M F B VCC Több-kimenetes, egyfázisú CMOS logika. VLSI

VCC VCC 2 VCC 1 VCC T1 p p p 2 p T6 p p nMOS logika A nMOS logika Uki B n n C1 C3 C4 C2 1 2 n n n n T8 1-szegmens 2-szegmens 1 Pseudo kétfázisú logika 1 t UC2 UC2 C2 kialakulása: T8 nyit t t0 t1 Inv2 átvált, T6 nyit T1 nyit, C1 töltődik, T8 még nem zárt le VLSI

VCC VCC 3 1 p p Uki n 4 n 2 C2 nMOS logika nMOS logika C1 n n TARTÁS TARTÁS ELŐ ELŐ ELŐ ELŐ KIÉ KIÉ KIÉ KIÉ TARTÁS TARTÁS A klasszikus négyfázisú logika VLSI

Kisfogyasztású logikai rendszerek a) kapacitások töltése/kisütésekor fellépõ joule-veszteség. A kapacitív áramokból adódó átlagos disszipáció nem adiabatikus átkapcsolásoknál, (E az óraciklusok alatt várható átkapcsolások száma): b) keresztirányú áram. Elhanyagolják, tekintettel arra, hogy az igen gyors jel-felfutások következtében a keletkezõ áramtüske idõtartama igen rövid s így az átlagos teljesítmény is alacsony a kapacitást töltõ áramok mellett. c) küszöb-alatti (szivárgási) áramok. VLSI

A fogyasztás csökkentésének eszköz-szintû lehetõségei Méretcsökkentés Küszöbfeszültség csökkentés, . dual-threshold-megoldás Tápfeszültség (Vdd) lecsökkentés.Zajvédettség, statikus (szivárgási) áram, BiCMOS, szint-áttevõ (transzlátor) áramkörök. Szigetelõ-anyagú hordozó. A fogyasztás csökkentésének kapcsolás-szintû lehetõségei Speciális kialakítású dinamikus logikák pl. a nem kritikus kapukat a késleltetés rovására lassabb, de kisebb teljesítményû kapukkal helyettesítik Adiabatikus töltés. Az adiabatikus töltés lényege, hogy a CL kapacitást a rámpa-alakú töltõ-feszültség eredményeképpena soros ellenálláson (R) keletkezõ (joule) veszteség a töltés ideje (T) megnövekedésének arányában lecsökken és ezzel a keletkezett disszipáció is. VLSI

Adiabatikus töltés. Az adiabatikus töltés lényege, hogy a terhelő-kapacitást a rámpa-alakú feszültséggel töltjük, s így a soros ellenálláson keletkezõ(joule)veszteség és ezzel a disszipáció lecsökken, Az ún. 2N-2P típusú adiabatikus elven mûködõ inverter hátrányos oldala, hogy Y=1 esetén afázisjel visszafutásakor a feltöltött C2 kapacitás csak Vth,p értékig sül ki, mivel ezt követõen T2 lezár. VLSI

Töltés-visszahúzásos (retractile) kapcsolások Négyfokozatútöltés-visszahúzásos (retractile) kaszkád kapcsolás, a fázisjelek „ölelkezõ” elrendezése; meg kell várni az õt követõ összes fokozat kiértékelését és visszahúzását. VLSI

Pipeline-működésű adiabatikus logika A 1 fázisjel felfutásakor az F logikai függvénynek megfelelõen a C1 kapacitás vagy töltõdik (adiabatikusan), vagy nem. Az F blokk CMOS transzfer gate-ekbõl épül fel. A1 fázisjel visszafutása elõtt aktíválódik a 2 fázisjel, amely a G logikai függvénynek megfelelõen, az elõzõhöz hasonlóan tölti (vagy nem) a C2 kapacitást. Ennek befejeztével a G-1 inverz logikai függvény gondoskodik arról, hogy a 1 fázisjel visszafutása során a C1 kapacitás adiabatikusan kisüljön. Pipeline logika elõnye, hogy a fokozatok mûködési ideje nem lapolja át egymást. VLSI

Rezonáns áramkörök Forgótekercses elrendezés, minor-minor V1 ...V4 jelek. V1=1 C12=1 és C11=0 esetén V1-el vezérelt transfer gate a 1 pontot a tekercs egyik végére, egy hasonló áramkör pedig a tekercs másik végét a 3 pontra kapcsolja, C12 töltése a tekercsen keresztül kisül és a rezonáns kör következtében feltölti a C11-et. A következő fázisban V2 =0 lesz, ami C11 -et átmenetileg VDD-re kapcsolja (a veszteségek pótlására). A mûködés során a töltésnek ez a "hintázása" valósul meg, a V1 ...V4 jelek ütemének megfelelõen körbeforogva. VLSI

A fogyasztás csökkentésének rendszer-szintû lehetõségei Órajel optimalizálás (clock-skew optimization); azonos idõpillanatban történõ átkapcsolása miatt mind a táp-, mind a földvezetéken nagy rövid-idejû áramlökések jönnek létre, teljesítmény-veszteség lép fel; a csúcsot idõben széthúzzák. Memóriák. Array-k (sub-block) , a hozzáférési idõ rovására Data Ordering Problem with Inverson (DOPI), az átvitel elõtt az adatot összehasonlítják az elõzõ átvitt adattal és ennek eredményeképpen, ha a bekövetkezõ átváltások száma nagy, akkor az invertált adatottovábbítják (jelzõ-bit). Hamming-távolság. "Resequencing": az átviendõadatokat (blokkok) átrendezi és egyben esetenként invertálja olyan módon, hogy az egymást követõ szavak Hamming-távolsága a minimális értékû legyen. A várható fogyasztás meghatározásának módszerei Teljeskörû szimuláció. Monte Carlo analízis. Particionálás.. VLSI

Összeadó áramkörök Gi= AiBi generate, Pi =Ai+Bipropagate Optimalizálás: elemszámot (chip felület) végrehajtási idő, minimális teljesítmény-felvétel VLSI

Transzfer gate-es logikával megvalósított összesadó. Ci Bi p p p n AI Bi Si+1 p n n n Ai p p p n Ci+1 p n n Ai n AI Bi Ci VLSI

Domino CMOS logikával megvalósított összesadó. Átvitel új értéke: Összeg új értéke: Átalakítás után: VCC VCC p p Si Ai Ai Ai Bi Ai Ci Bi Bi Ci Bi P-logika Ci+1 Ci N-logika VLSI

Carry look-ahead Domino CMOSáramkör. VCC Static current Ci+2 Cpre Pi+2 Gi+2 Pi+1 Gi+1 Ci VLSI

VCC VCC VCC VCC Pi Pi+1 Pi+2 Pi+3 Ci+1 Ci+2 Ci+3 Ci+4 Ci Gi Gi+1 Gi+2 Gi+3 Dinamikus Manchester-carry áramkör Átvitel gyors előállítása, 4x Domino + transzfer-gate Cpre hamis kisülésének feltétele: Ci=1 és Pi=1. Ekkor viszont alapján Cpre=Ci+1=0, vagyis nincs kisütés. Cpre VLSI