DNC, GEC & Non-linear interpolation

250 likes | 464 Views

DNC, GEC & Non-linear interpolation. A Review of ”A Digitally Enhanced 1.8V 15-bit 40-MSample/s CMOS Pipelined ADC”[1] & ”Background Digital Calibration Techniques for Pipelined ADC’s”[2]. Pipelined ADC review. Non-linearities in DAC levels cause harmonic distortion

DNC, GEC & Non-linear interpolation

E N D

Presentation Transcript

DNC, GEC & Non-linear interpolation A Review of ”A Digitally Enhanced 1.8V 15-bit 40-MSample/s CMOS Pipelined ADC”[1] & ”Background Digital Calibration Techniques for Pipelined ADC’s”[2]

Pipelined ADC review • Non-linearities in DAC levels cause harmonic distortion • Common solution: Try to randomly distribute non-linearities in DAC so energy is spread out in the frequency spectrum • Interstage gain errors reduce SNDR/SNR • Solution: Apply correction gain digitally

Detecting a known signal component in the output of an unknown system Mean of td = 0 • Td with a mean of zero: • Periodic signal • Pro: Can have a small N since power of td is evenly distributed in time • Con: Delta function in the frequency domain • White noise signal • Pro: Flat power density spectrum • Con: Need large N, ideally N=∞

A Digitally Enhanced 1.8V 15-bit 40-MSample/s CMOS Pipelined ADC

Outline • Dynamic Element Matching (DEM) • DAC Noise Cancellation (DNC) • Gain Error Correction (GEC) • Bootstrapped Switches • Timing

Dynamic Element Matching (1) • Errors in DAC paths cause signal dependent error • Signal dependent error => Distortion

Dynamic Element Matching (2) • Scrambler randomly selects a sequence of Sn such that Vout equals (1) • The error, e, is uncorrelated with the input signal if it is done correctly • This will effectively spread DAC noise power in the frequency spectrum (1)

DEM encoder from [1] • With DEM encoder from [1] it can be shown that DAC noise inherits statistical properties of the pseudorandom sequence used in DEM • This can be used to estimate the mismatch in the DAC paths • Each path error is related to a specific pseduorandom sequence DAC path errors Known sequences

DAC Noise Cancellation • Detect presence of known pseduorandom signal, s[n], in output, u[n] + εs[n], by calculating the covariance • Estimate DAC path error, ε, from covariance • Multiply psedurandom sequence by path error estimate and subtract from output • Repeat for all DAC paths

Gain Error Calibration (GEC) from [1] • Estimate gain error from covariance of digitized residue and pseudorandom signal • Assuming small ε =>(1 + ε ) ≈ 1, multiply digitized residue by gain estimate and subtract from output

Bootstrapped switches • Used on continous-time input sampling switches • Increased linearity • Used on switches connected to mid-supply or time-constant matching constrains • Reduced resistance

Timing • First stage amplification is most important • Steal time for first stage Flash from second stage

Results from [1] • SFDR is improved by 12dB with DNC and GEC enabled • SNDR is improved by 20dB with DNC and GEC enabled Signal Without calibration With calibration

Background Digital Calibration Techniques for Pipelined ADC’s

Outline • Error Model • Calibration Method • Non-linear Interpolation • Quantization Effects on Interpolation

Positive calibration voltage Negative calibration voltage Error measurement • Measure gain error in each stage by applying known calibration voltage, Vcal-i

Simulation results • Simulated performance (DNL & INL) with and without gain calibration

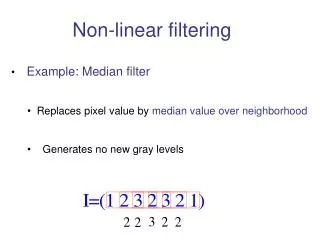

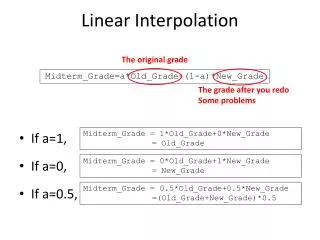

Non-linear Interpolation • Uses fitting of high order polynomials to estimate missing sample. • Uses causal and noncausal taps Normalized coefficients

Non-linear Interpolation • Limits input bandwidth of converter below Nyquist Fin < ½ Nyquist Fin < Nyquist

Non-linear Interpolation • Interpolation error depends on the number of taps • Achieve higher bandwith with a certain error by using more taps

Quantization Effects on Interpolation • Quantization noise limits performance of interpolation • Each tap adds quantization noise to total noise power • Limits the number of taps Variance vs number of taps

References • Eric Siragusa & Ian Galton; ”A Digitally Enhanced 1.8V 15-bit 40-MSample/s CMOS Pipelined ADC”; IEEE Journal of Solid State, Vol. 39, NO. 12, December 2004 • Un-Ku Moon & Bang-Sup Song;” Background Digital Calibration Techniques for Pipelined ADC’s”; IEEE Transatctions on Circuits and Systems-II, Vol. 44, NO. 2, Febuary 1997