1 차 설계 결과 보고서 Nand 를 이용한 소인수 분해기

회. 로. 해. 석. 1 차 설계 결과 보고서 Nand 를 이용한 소인수 분해기. 및. 논. 리. 회. 발표자 2004731010 권 민 형 2004731200 박 인 규 2005730172 홍 진 표 2007732005 고 경 태. 로. 7 조. 실. 험 1. 목 차. 1. 설계 목적 및 과정. 2. 블록도 및 회로도. 3 . 설계 중간과정. 4. 설계 중간과정의 성과. 5. 최종 설계 완성 사진.

1 차 설계 결과 보고서 Nand 를 이용한 소인수 분해기

E N D

Presentation Transcript

회 로 해 석 1차 설계 결과 보고서 Nand 를 이용한 소인수 분해기 및 논 리 회 발표자 2004731010 권 민 형 2004731200 박 인 규 2005730172 홍 진 표 2007732005 고 경 태 로 7조 실 험1

목 차 1. 설계 목적 및 과정 2. 블록도 및 회로도 3 . 설계 중간과정 4. 설계 중간과정의 성과 5. 최종 설계 완성 사진 6. 비용,역할 분담 및 제작 일정

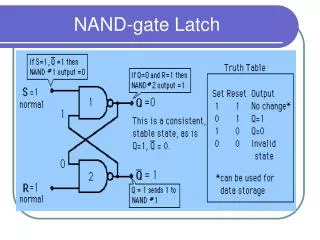

1-1.설계 목적 ★1~10까지의 숫자를 소인수 분해하여 소인수의 지수를 표시하는 회로를 설계한다. ★ 설계 시 유의사항 1. Nand gate 만을 사용한다. 2. 게이트 수를 최소화 한다. 3. 실현 가능한 옵션을 설치한다.

1-2.설계 과정 • 입력 8 x 3 인코더 2개를 사용하여 16 x 4 인코더를 만들어 10개의 스위치를 이용해 입력한다. (옵션부) • 논리 회로부 Nand만을 사용하여 논리회로를 구현한다. 2의 지수와 3의 지수는 2비트, 5의 지수와 7의 지수는 1비트로 취급한다. • 출력 디코더를 이용하여 논리회로부의 출력을 7-세그먼트로 표현한다.

1-3.카르노맵 2의 지수 첫번째 a =C D C D

1-3.카르노맵 2의 지수 두번째 a =C D + A D C D A D

1-3.카르노맵 3의지수 첫번째 a = A D A D

1-3.카르노맵 3의지수 두번째 C ( B D B D ) a=B C D + B C D

1-3.카르노맵 5의지수 a = A C + B C D A C B D C A C X C B D = X

1-3.카르노맵 7의지수 a=BCD B D C X C B D = X

2-1.전체 회로의 블록도 스위치 입력부 (옵션부) 논리회로부 세그먼트 출력부

2-2. 회로도 16 x 3 인코더를 이용한 스위치 입력부의 설계

2-2. 회로도 Nand 수정 이전의 주 회로도

2-2. 회로도. Nand Gate 를 사용한 주 논리회로부

2-2. 회로도 7-세그먼트를 이용한 출력부

2-2. 회로도의 파형확인 스위치 입력부의 파형 확인 NAND논리회로부의 파형 확인

3-1. 설계 중간과정 • 2의 지수 출력 확인 • 3의 지수 출력 확인 17

3-2. 설계 중간과정 • 5의 지수 출력 확인 • 7의 지수 출력 확인

3-3. 설계 중간과정 • 16 x 8 인코더를 사용한 • 스위치 부의 구현

논리회로부에 비해 옵션이 더 복잡한 배선으로 납땜에서의 문제 예상문제 예상 • 각 지수부분의 구현 4.중간과정에서의 성과 • Nand 를 사용한 논리회로도가 제대로 설계됨을 확인 할 수 있었음. • 최종적으로 필요한 Gate의 수 및 칩의 개수 확인. • 옵션으로 사용 할 스위치 입력부와 세그먼트 출력부의 구현

5-1.최종 설계 세부과정 • 출력부를 결선한다. 그 동안 옆에서 만능기판에 논리회로부 구성 및 테스트를 통해 최종 논리 회로 확인 및 각 IC의 작동 유무를 확인한다. • 결선한 출력부를 TEST 한다. • 논리회로부를 결선한다. 그 동안 옆에서 만능기판에 스위치 부를 결선 및 테스트 한다. • 결선한 논리회로부를 TEST한다. • 스위치 부를 결선한다. • 스위치부 – 논리회로부 – 출력부 를 같이 결선한다.

5-2.고장점검 및 해결 과정 1.논리 회로 부 출력>>3의 지수 디코더 입력으로의 결선확인 2. 위 확인 후 논리회로부의 회로 도 대로 결선 되었는지 확인 3. 위 확인 후 회로도를 만든 초기 수식자체를 확인 4. 위 확인 후 논리 회로 부 IC의 모든 GATE의 동작 각각 확인. 5. 하나의 IC의 4개중 1개의 게이트 동작 오류 발견 >> 문제 해결. 논리회로 부 TEST에서 10 출력 때 3의 지수 출력 오류 발견.

5-4.옵션 총정리 1. 스위치 옵션 2. 밑 수의 세그먼트 출력

5-4.옵션 총정리 3. 전체 회로 전원 4. On/Off 겸 에러 출력 Led

Lucky 7조, 감사합니다.