Continuous-Time Laser Programmable Analog Array for Radiation Environments

This paper presents the design and implementation of a radiation-tolerant Laser Programmable Analog Array (LPAA) utilizing advanced silicon-on-sapphire technology. It outlines the technical approach, including the architecture of the Configurable Analog Block and detailed descriptions of the laser via technology and amplifier design. The LPAA showcases a fully differential circuit topology, continuous-time operation, and low parasitic capacitive effects, making it suitable for high-performance analog applications in challenging radiation environments. The paper also discusses the lessons learned during the development process.

Continuous-Time Laser Programmable Analog Array for Radiation Environments

E N D

Presentation Transcript

Continuous-Time Laser Programmable Analog Array for Radiation Environments MAPLD September 8 – 10 2004 Anthony L. Wilson ATK Mission Research 5001 Indian School Road NE Albuquerque, NM awilson@mrcmicroe.com Ji Luo, Joseph B. Bernstein, J. Ari Tuchman, Hu Huang, Kuan-Jung Chung University of Maryland 2100 Marie Mount Hall College Park, MD

Outline • Introduction – Goals and Objectives • Overview of Technical Approach • Process Description • “Switch” Description • Amplifier Design • Configurable Analog Block (CAB) Architecture • Laser Programmable Analog Array (LPAA) Architecture Description • How to get from Point A to Point B - Router Development • User Interface • Lessons Learned Wilson B117/MAPLD 2004

Introduction • Definitions • LPAA: Laser-Programmable Analog Array • CAB: Configurable Analog Array • FBFTFN: Fully Balanced Four-Terminal Floating Nullor • PRA: Programmable Resistor Array • PCA: Programmable Capacitor Array • SOS: Silicon-on-Sapphire “… a monolithic collection of analog building blocks, a user-controllable routing network used for passing signals between building blocks…” E. Pierzchala, et al., “Field-Programmable Analog Arrays”, Kluwer Academic Pub., 1998 Wilson B117/MAPLD 2004

Goals/Objectives • Design of a radiation tolerant programmable analog array • Design of an high performance analog array • Demonstration of the laser via technology • Demonstration of Peregrine UTSi™ CMOS SOS technology for analog applications • Development of an analog router for analog arrays Wilson B117/MAPLD 2004

Overview of LPAA Design • Array style architecture • Fully Differential Circuit Topology • Voltage and Current Mode Capability • CMOS Silicon-on-Sapphire Technology • Continuous-Time Operation • Parasitic Aware Analog Router • Low Resistant Laser Via Technology Wilson B117/MAPLD 2004

Process Description • Fully depleted CMOS/SOS (silicon on sapphire) processing technology • Has only a small source/drain to body. Reduces parasitic capacitance and produces a higher speed technology • The threshold voltage can be easily tailored and values of 0.0, 0.3, and 0.8 volts are available in the technology • The thin gate oxide has high intrinsic radiation hardness • Fully depleted body exhibits no back channel effects • There is no possibility of radiation induced leakage current between adjacent devices • Linear MIMCAP available • High Value resistor available Wilson B117/MAPLD 2004

Radiation Performance of the UTSi Transistors Pre/Post Radiation Performance UTSi NMOS transistor.(Data courtesy of Peregrine Semiconductor) Pre/post Radiation Performance of UTSi PMOS transistor.(Data courtesy of Peregrine Semiconductor) Wilson B117/MAPLD 2004

M2 M1 link “Switch” Description - Laser Via Technology • The most reliable type of link that can be formed is based on the principle that two adjacent (horizontally or vertically) metal lines can be exposed to an infrared (IR) laser pulse and thermal expansion of the metal fractures the intervening dielectric. Rapidly expanding molten metal quickly flows through the resultant crack and electrically connects the lines • The structure is designed using the top two layers of metal in the target process • Laser via structures can be located directly over transistors since the active area is shadowed by the upper metal annulus and, at the laser energy levels needed for link formation • Hermeticity, radiation hardness, and compatibility with advanced CMOS fabrication processes • Laser vias exhibit the same hardness to total ionizing dose and to energetic heavy ions as normal vias and normal interlevel dielectric W. Zhang, et al., “Reliability of Laser-Induced Metallic Vertical Links”, IEEE Trans. on Adv. Pack., vol. 22, no. 4, pp. 614-619, 1999. FIB Cross-section View Wilson B117/MAPLD 2004

Laser Via Energy Profile • 8 different test patterns • Each block was a continuous chain of links that would be connected using the laser formed vias • The preliminary evaluation achieved fewer than one failed link per 20,000 links across the entire laser energy window from 0.30 to 0.70 mJoules • This energy window corresponds to the amount of laser energy deposition is needed to form the via • Formed via has less than 0.8 ohms of resistance Wilson B117/MAPLD 2004

Amplifier Description • Differential difference input stage • Inner and outer CMFB circuits (not shown) • Bias circuit included (not shown) • Provides voltage and current output nodes simultaneously • Fully balanced fully differential architecture • Fully Balanced Four-Terminal Floating Nullor (FBFTFN) Amplifier Structure • Class AB output stage Wilson B117/MAPLD 2004

FBFTFN Flexibility • Support configurations of a “universal active element” H. Schmid, “Approximating the Universal Active Element”, IEEE TCAS-II, vol. 47, no. 11, pp. 1160-1169, 2000 Wilson B117/MAPLD 2004

FBFTFN AC Performance • Simulation plot of the FBFTFN circuit • Shows gain-bandwidth = 15 [MHz] • Shows phase margin = 67 [deg] Wilson B117/MAPLD 2004

Voltage Amplifier Simulation • FBFTFN configured as a voltage amplifier • Feedback resistors are varied for various gains • Shows reduced bandwidth for increased gain (as expected) Wilson B117/MAPLD 2004

Transconductor Amplifier Simulation • FBFTFN configured as a transconductor amplifier • Variable gains • Show constant bandwidth for various gains • Bandwidth smaller than voltage amplifier Wilson B117/MAPLD 2004

Sallen-Key Filter Simulation • Bandpass Filter simulation • FBFTFN configured as a fully differential 2nd generation current conveyor Center Frequency = 837 kHz Q = 7.07 Wilson B117/MAPLD 2004

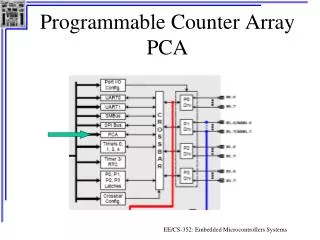

PRA and PCA Descriptions • Programmable Resistor Array (PRA) • Allows of single, parallel and series connnection • Can select multiple individual resistors if needed • Can short paths for direct connections • Programmable Capacitor Array (PCA) • Similar to PRA • No short connectors Wilson B117/MAPLD 2004

CAB Design • Each CAB uses 1 FBFTFN • 4 inputs/4 outputs • 4 PRAs • 4 PCAs • Lines in read = 8 track buses • Boxes represent laser formed via arrays used for routing Wilson B117/MAPLD 2004

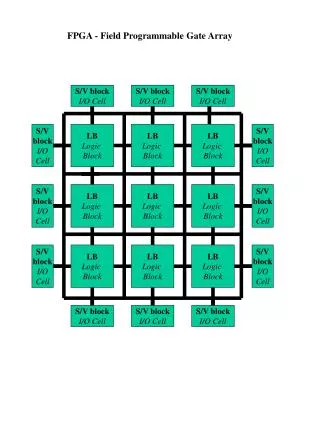

Architecture Description • 4x2 array of CABs • 8 tracks per channel • Switch Box • Connection Box • Dedicated routing for power supplies • Dedicated routing for bias and common mode voltages • Input pads on left and bottom • Output pads on right and top Wilson B117/MAPLD 2004

Analog Array Architecture Description Assumptions: • The Analog Array has the coordinate system defined from (0, 0) to (3, 5). The four corner positions, (0, 0), (0, 5), (3, 0), (3, 5), are blank areas. • Each X or Y directed channel belongs to the pad or CAB right below it, or on the left to it, having the same coordinates. • The legal routing connections are: • LHS pads can connect to all the tracks in channel y (0, 1); RHS pads can connect to all the tracks in channel y (2, 1). • Bottom row pads can connect to all the tracks in channel x (1, 0); top row pads can connect to all the tracks in channel x (1, 4). • Input CAB pins can connect to tracks in the channels immediately on the left, top and bottom of the CAB; output CAB pins can connect to tracks in the channels immediately on the right, top and bottom of the CAB. • Tracks in the horizontal channel can connect to tracks in vertical channel if a switch is available at the intersection. • Direct connections between CAB pins are not allowed; direct connections between PADs and CAB pins are not allowed. • Dogleg is not allowed, i.e., CAB pin cannot be acted as intermediate vertex to route a net. Wilson B117/MAPLD 2004

Analog Array Architecture Diagram • Auniform architecture • Channel Width: 8 • Connection Block Flexibility:8 • Switch Block Flexibility: 4 • Segment Length: 4 Wilson B117/MAPLD 2004

Connection and Switch Boxes • Connection box used to achieve a connection flexibility of 8 • Switch box chosen to achieve a connection flexibility of 4 • Alternate parity for switch boxes (Pattern 1 and Pattern 2) used to increase routability Wilson B117/MAPLD 2004

4 12 3 11 CAB3 CAB1 9 1 10 2 c e d f 8 16 15 7 CAB2 CAB4 5 13 14 6 g h a b Router Development • Definition of routing: Given a netlist along with a placement of the CABs and IO cells, to route all the nets on the given FPAA architecture without exceeding the total available routing resources and without overly degrading the performance of the circuit (Goals: (1) Avoid congestion; (2) Satisfy a set of performance constraints) • Routing Problem - Graph Problem Routing Resource Graph (RRG) • Vr : I/O pins, wire segments • Er : feasible connections • Routing Resource type: pin, pad and track (PPT number) find a set of disjoint trees T={T1,…Tn}. Each tree spans all the terminals of the net with “minimum” cost: Minimum Steiner Tree (MST) Problem: NP-Complete Wilson B117/MAPLD 2004

LPAA Router Description • Analog array router based on the Pathfinder Negotiated Routing Algorithm • Completed a routability-driven router • Although called routability-driven, the router resolves the congestion and attempts to find the “shortest path”. • Therefore the accumulated parasitic (especially the loading capacitance and serial resistance) are automatically kept to a near minimum value, along with the wave expansion process (breadth-first search). • The extremely small parasitic associated with the laser via, this router is sufficient for this relatively small-scaled analog array LPAA Design Flow Wilson B117/MAPLD 2004

Loop over all sinks Loop over all nets PQ <= RT Pathcost(n)= base(n) RT(i)=φ? Y Sink in RT? Y N Rip_up RT(i) Update p(n) RT(i)<=net(i) Source N Init Dequene (m) PQ Enquene fanout (m) Update pathcost=pathcost(m) + Base(n) Route Net i Sink found ? All nets done? N N Backtracing Update p(n) Update h(n) Y Y Overuse? MAX_ITER? N Y Finish all sinks? Y END N Pathfinder Negotiated Routing Flow Wilson B117/MAPLD 2004

User Interface • JavaTM chosen as language – cross platform • Direct input from user • Allows user to perform local connections within CAB • Allows user to perform CAB-to-CAB connections • Spice netlist creation • Router compatible netlist file creation Wilson B117/MAPLD 2004

Screenshot of User Interface • Early Development Phase Wilson B117/MAPLD 2004

Lessons Learned • Reticle Size Problem • Floor planning a must • Optimizations: • Add additional parameters to the router code cost function • Segmentation would need further addressing for larger arrays • Adding switched-capacitor implementation for increased flexibility • Programmable amplifier bias • Inclusion of voltage reference • Separation of amplifier and buffer stage Wilson B117/MAPLD 2004