Dynamically Programmable Array Architecture

This document outlines the evolution of dynamically programmable array architectures, focusing on the contributions made by Robert Heaton at Texas Instruments. It delves into the design of ARM processors, geometric compression algorithms, and the physical layer protocols for 100BaseT4 and Gigabit copper LAN technologies. It highlights the unique features of the two-dimensional mesh architecture, including bi-directional buses and hierarchical addressing, in addition to addressing future steps in VHDL modeling and primitive assembler tools for PLUs.

Dynamically Programmable Array Architecture

E N D

Presentation Transcript

Dynamically Programmable Array Architecture Robert Heaton Obsidian Technology

Personal Background • Texas Instruments first gate array • Led ARM processor development team • Geometric compression algorithms • 100BaseT4 100Mb LAN physical layer • Gigabit copper LAN analog

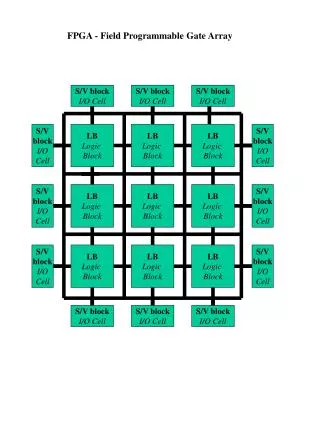

Mesh of Trees PLU PLU PLU PLU • Busses are BI-directional • 2 Cycles to exchange data • Separate X and Y dimensions • Diagonal routing not directly supported • PLU’s difficult to program to take advantage of structure PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU

Two Dimensional Mesh PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU

Mesh Routing Unit • Full Duplex connect busses • Each PLU node controls its source ports via a 2 bit local or 10 bit hierarchical address • Innate broadcast support • Any node may listen to any other input to the cluster • Hierarchical node addressing must not clash • Ring connections OK PLU PLU Routing Unit (RU) PLU PLU

Mesh Routing Unit • Any PLU can listen to any other • Any two pairs can exchange data PLU PLU Routing Unit (RU) PLU PLU

Mesh Routing Unit • Local or Hierarchical ring connections • Any number of PUs can be connected in series/parallel PLU PLU Routing Unit (RU) PLU PLU)

4x4 Hierarchical Cluster PLU PLU PLU PLU RU RU PLU PLU PLU PLU RU PLU PLU PLU PLU RU RU PLU PLU PLU PLU

RU Hadr L0adr L1adr L2adr A=2, 1, 2, x 4x4 Cluster Routing PLU PLU PLU PLU RU RU PLU PLU PLU PLU A=1 0 1 RU1 2 3 PLU PLU PLU PLU PLU 1 RU PLU PLU PLU PLU PLU

PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU RU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU Hadr L0adr L1adr L2adr a0 a7 A Mesh Routing Hierarchy PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU RU RU RU RU RU RU RU RU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU RU1 RU1 RU1 RU1 PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU RU RU RU RU RU RU RU RU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU • 256 PUs • 4 Levels of hierarchy • Hadr: up level till • L0adr: local address • L1adr: level 1 address • L2adr: level 2 address RU2 RU2 RU1 RU1 RU1 RU1 RU3 PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU RU RU RU RU RU RU RU RU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU RU1 RU1 RU1 RU1 PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU RU RU RU RU RU RU RU RU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU PLU RU2 RU2 RU1 RU1 RU1 RU1

PLU Overview • Simple data path functionality • Primitive control options • Wide instructions control data path function and operand routing • Conditions may be inverted for “repeat until” or “Branch If” control • Very primitive address arithmetic • 32 or less instructions in program

Design Tools • Tanner: • Schematic entry, logic simulation, custom layout, layout verification. • Circuit Simulation. • PC & Sun platforms. • MOSIS Libraries. • Mentor Graphics: • VHDL compilation and simulation.

Initial PLU Design Tools • PLU Assembler / Compiler • Architecture mapping • Simulation modeling and environment • Global resource allocation

Open Issues • PLU Data path width • Complexity of PLU operations • RU Trunking • Number of contexts per PLU • Power reduction strategies • Flexible context RAM partitioning • PLU synchronization

Next Steps • VHDL Modeling of Architecture • Primitive assembler tools for PLUs • Selection coding and simulation of applications • Architecture tuning • Layout and verification of complete DPA