Plato Front End Electronic

Plato Front End Electronic. Alan Smith UCL/MSSL. Simulation. Management. Software. Engineering/ Requirement/Budget. Optic. Interfaces. Electrical. Thermal/Mecha. AIT. Product Assurance. Payload Management . 200 001. 200 000. System. CAMERA. Data Processing System. 230 000.

Plato Front End Electronic

E N D

Presentation Transcript

PlatoFront End Electronic Alan Smith UCL/MSSL

Simulation Management Software Engineering/ Requirement/Budget Optic Interfaces Electrical Thermal/Mecha AIT Product Assurance Payload Management 200 001 200 000 System CAMERA Data Processing System 230 000 210 000 220 000

Simulation Management Software Engineering/ Requirement/Budget Optic Interfaces Electrical Thermal/Mecha AIT System 210 000 Camera Engineering DPS Engineering Payload AIV 212 000 211 000 213 000 Simulations Simulations Verification Strategy 212 100 211 100 213 100 Requirements / Budget Requirements / Budget 212 200 211 200 Integration &Test Plan 213 200 Interfaces Data Process Algo 211 300 212 300 Instrument & Payload AIT 213 300 Optical Design 211 400 Interfaces 212 400 Electric Architecture Monitoring & Control Coupling tests 212 500 213 310 211 500 Functional Acceptance Mecha-Therm. Arch. 211 600 213 320 CCD requirement support Calibration 213 330 211 700 AIV Requirementsat PLM level 213 400

Simulation Management Software Engineering/ Requirement/Budget Optic Interfaces Electrical Thermal/Mecha AIT CAMERA 220 000 223 000 Telescope Optical Unit Focal Plane Assembly N-Front-End Electronic F- Front-End Electronic Assembly Integration &Tests AlternativeF-FPA 221 000 Auxiliary Electronic Unit 224 000 225 000 223 002 222 000 226 000 Integration Quality Assurance Product Assurance Product Assurance Product Assurance Product Assurance Product Assurance 224 001 221 001 223 001 225 001 223 004 222 001 223 100 224 100 AIT Plan 225 100 Engineering Engineering Engineering Engineering 222 100 221 100 AIT Procedure 225 200 Thermal design Optical design Electrical design Electrical design 221 110 222 110 223 110 224 110 GSE Engineering & Validation Structure design 222 120 Structure design 221 120 225 300 Thermal design Thermal design 223 120 224 120 Interfaces 222 130 Thermal design 221 130 Housing design Housing design 223 130 224 130 Optical design Requirements &Budget 225 310 Interfaces 221 140 222 140 Interfaces Interfaces 223 140 224 140 Thermal design 225 320 Requirements &Budget AIV 221 150 222 150 Requirements &Budget Requirements &Budget Mechanical design 225 330 223 150 224 150 Straylight 221 160 Structure Electrical design 222 200 225 340 AIV AIV 223 160 224 160 AIV 221 170 Thermal parts 222 210 N-Housing GSE Housing F-Housing 223 200 225 400 224 200 223 500 N&F FPA AIT 222 300 Structure 221 200 Thermal parts Thermal parts 224 210 223 210 OGSE Thermal parts 223 510 225 410 GSE 222 310 Baffles 221 210 F-Board procurement Board procurement TGSE N-Board procurement 225 420 223 600 223 300 224 300 Thermal parts 221 220 MGSE 225 430 N-AIT F-AIT AIT 223 400 223 700 224 400 EGSE 225 440 Lenses 221 300 GSE GSE GSE 223 410 223 710 224 410 AIT 225 500 N-TOU AIT 221 400 Qualification tests 225 510 GSE 221 410 Acceptance tests 225 520 F-TOU AIT 221 500 AIT Prototype & Expertise 225 600 Filters 221 510 221 520 GSE

Simulation Management Software Functional Validation Software Functional Validation Software Engineering/ Requirement/Budget 235 800 234 800 Optic Interfaces GSE GSE 234 810 235 810 Electrical Thermal/Mecha AIT Data Processing System 230 000 234 000 235 000 236 000 Data Processing Algorithms 231 000 N-DPU Application Software 232 000 Main Electronic Unit 233 000 Instrument Control Unit Fast-DPU Assembly Integration & Tests Product Assurance 232 001 233 001 Product Assurance 234 001 Product Assurance 235 001 Integration Quality Assurance Product Assurance 236 001 AIT Plan 236 100 231 100 Engineering Engineering Engineering 233 100 PSF modeling Software development 235 100 234 100 232 100 AIT Procedure 236 200 Photometry methods 231 200 Requirements &Budget Requirements &Budget Requirements &Budget 235 110 233 110 234 110 Software Validation 232 110 GSE Engineering Binary mask 231 210 236 300 Electrical design Electrical design Electrical design 235 120 233 120 234 120 Weighted mask 231 220 Software Functional Validation GSE 236 400 232 200 Housing design Housing design Housing design 231 230 LSF fitting 235 130 233 130 234 130 AIT 236 500 Centroiding methods Thermal design Thermal design Thermal design 231 300 GSE 235 140 232 210 233 140 234 140 Background determination Interfaces Interfaces Interfaces 235 150 233 150 234 150 231 400 AIV AIV 235 160 AIV 233 160 234 160 Target recognition 231 500 N-DPU boards 233 200 Jitter correction 231 600 F-DPU boards F-DPU boards 234 200 235 200 Power Supply 233 300 Discontinuity & trend correction Power Supply Power Supply 234 300 235 300 231 700 Boot software 233 400 Boot software Boot software 234 400 235 400 Outlier rejection 231 800 Housing 233 500 Housing Housing 234 500 235 500 Performance Tests 231 900 AIT hardware 233 600 AIT hardware AIT hardware 234 600 235 600 Light-centroid curves 231 910 GSE 233 610 GSE GSE 234 610 234 610 Jitter modeling 231 920 F-DPU Application Software ICU Application Software 234 700 235 700 Software development Software development 234 710 235 710 Software Validation Software Validation 234 711 235 711

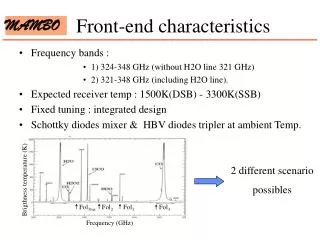

MSSL heritage in flight CCD readout electronics Eddington CCDs • For nearly 20 years MSSL has designed and built flight electronics for CCD imaging and spectroscopy instruments, including:- • XMM-Newton Optical Monitor • INTEGRAL Optical Monitor Camera • NASA SWIFT UV Optical Telescope • Hinode EUV Imaging Spectrometer • Hinode SOT CCD characterisation • NASA ‘MOSES’ experiment • Eddington demo Focal Plane Array • Gaia PEM Industrialisation • Euclid Vis-FPA Assessment Phase INTEGRAL OMC Gaia PEM Hinode EIS MOSES PLATO Consortium Meeting, MSSL

GAIA PEMESA industrialisation contract PLATO Consortium Meeting, MSSL

Plato CCD specifications • CCD format: 4510 x 4510, 18 x 18µm • Full Frame • Number readout ports per CCD: 2 • 4-phase • ADC speed: 4 Mpix/s • Peak storage: 1000 ke- • PRNU (1σ): 3-5% • ADC resolution: 14 bits • Line transfer time 80 µs • Readout time ~3s • Static power: 180 mW • Dynamic power: 1300 mW • Readout noise: <18 e- • No anti-blooming 1st CCD’s available 07/11; Before then CCD203-82 will be used; similar size, 4-phase device CCD203-82

Current Issues: Coping with more signal by using bloomed charge

Current Issues: Coping with more signal by using bloomed charge

CCD Radiation Effects • While L2 is a popular location for future science mission there are very few currently operating there. • Radiation effects are mission specific, PLATO ≠ GAIA, different CCD readout, higher sky background ... • CCD CTE is mission critical • Mission specific radiation studies are essential • Moreover, detailed analysis of the mitigation software required to account for the effects of radiation damage to allow recovery of the science performance

FEE Analogue design Phil Thomas PLATO Consortium Meeting, MSSL

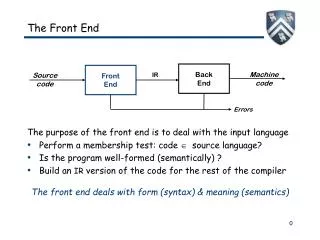

A typical analogue front end for CCD readout using ‘discrete’ circuit blocks VIDEO_E Clamp & sample CDS CM filter & source loads CCD output protect Row & Pixel clamp LP filter LP filter Buffer Preamp 16-bit ADC DUMMY_E VIDEO_F 4 CM filter & source loads Part of Bias & Clock hybrid SHDN, RD, CS, BUSY DUMMY_F Black level adjust Digital section Buffer CCD VIDEO_G CM filter & source loads CONVST DUMMY_G SPI DATA, CLK, CS 3 2 CDSCLP, CHGINJ 2 CHGDMP VIDEO_H CM filter & source loads PIXCLP DUMMY_H SUBSTRATE Electrical Verification Model for the Euclid Assessment Phase PLATO Consortium Meeting, MSSL

Candidate Analogue Front End IC • MSSL has identified a flight-qualified, dual Analogue Front End (AFE) IC. • One dual AFE IC can readout two CCD or APS sensor outputs. • The dual AFE IC incorporates Correlated Double Sampling (CDS) and Analogue-to-Digital Conversion. • The dual AFE has 14-bit resolution, operates from 3 to 40 Mpix/s, and consumes 212 mW at 4 Mpix/s for each port. • 14-bit resolution with guaranteed monotonicity is believed to be acceptable for PLATO (Walton, Catala). A 16-bit ADC has no measurable effect on the data. • A 14-bit ADC has a noticeable effect only for stars magnitudes M>~12. PLATO’s principal magnitude range is 8 to 11, so perhaps 14-bit resolution is acceptable. • The key requirements are monotonicity, repeatability and specified RMS noise. The Effective Number of Bits (ENOB) may not be such a good measure to assess the ADC for PLATO. PLATO Consortium Meeting, MSSL

Candidate Analogue Front End IC (cont.) • The dual AFE IC would save considerable board area and power, if it can be shown to achieve the required scientific performance. • Using the dual AFE IC the Fast FEE could use an identical architecture to the the Normal FEE. • However, power conditioning, CCD bias generation and clock driver circuitry will be still needed as part of the FEE, along with digital elements (clock sequencer, control, etc). • The dial AFE’s output is four-channels of LVDS serial data, consisting of seven differential signals. • If the dual AFE chip is used for PLATO there will be no need to multiplex 4 CCDs into a one pair of ADCs. Each 2-port CCD could have its own dual AFE chip. This is explained in more detail in the digital and system section. PLATO Consortium Meeting, MSSL

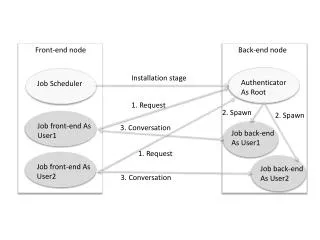

FEE Digital and system design Kerrin Rees PLATO Consortium Meeting, MSSL

N-FEE architecture (baseline) • One AFE per CCD • Reduced IC count • Measure of fault tolerance • Low power • Simple PLATO Consortium Meeting, MSSL

N-FEE architecture (backup) • One AFE with the CCD outputs buffered and multiplexed • High chip count • 16 anlg buffers required • 2 x 8:1 analogue muxes required • Reduced signal integrity • Less fault-tolerant PLATO Consortium Meeting, MSSL

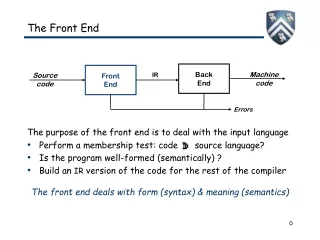

FPGA architecture • MSSL standardises on a WishBone bus internal FPGA structure • WishBone is an open standard for on-chip communications, used in FPGAs and ASICs • It is fairly high speed (one data transfer takes 2 clock cycles or 1 clock cycle in block transfer mode) • It is simpler than the commercial equivalents (AMBA, CoreConnect etc) • Low hardware overheads • Assuming the buffered SpaceWire architecture, with four AFE chips, the structure of the FPGA is as shown on the next slide. • Note that a different N-FEE architecture does not change the FPGA internal structure very much because the design is modular PLATO Consortium Meeting, MSSL

FPGA internal structure Note: The F-FEE could be identical, but the AFE interface receivers, frame buffers and their controller would be missing, placed in the F-DPU instead PLATO Consortium Meeting, MSSL

Initial link trade-off High numbers good; low numbers bad PLATO Consortium Meeting, MSSL

N-FEE to DPU Communications trade off • Conclusion • The option we recommend for the N-FEE is a single SpaceWire link with local frame buffering • Board area study required for this option • The bespoke link (direct AFE output) gives a very simple forward path for an F-FEE PLATO Consortium Meeting, MSSL

CCD Calibration Sequence Back fill Removal CCD Arrival Traveller Initiated Assembly Pump Calibration Store Auto Process Store Pack Deliver Archive Review Data Input Report generation CCD Data pack Review ~140 CCDs will be calibrated

Issues • SpaceWire • FEE mass and size • Power architecture • Radiation effects

Any questions? PLATO Consortium Meeting, MSSL