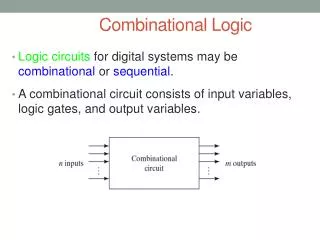

COMBINATIONAL LOGIC

COMBINATIONAL LOGIC. Read 4.1, 4.2. Example Gate: COMPLEX CMOS GATE. Propagation Delay Analysis - The Switch Model. Analysis of Propagation Delay. What is the Value of R on ?. Computing R on for t PHL , for an inverter. Numerical Examples of Resistances for 1.2 m m CMOS.

COMBINATIONAL LOGIC

E N D

Presentation Transcript

COMBINATIONAL LOGIC Read 4.1, 4.2

What is the Value of Ron? Computing Ron for tPHL , for an inverter

Numerical Examples of Resistances for 1.2mmCMOS See Example 4.2, table 3.3

• for symmetrical response (dc, ac) • for performance V DD B 12 6 A Input Dependent 12 C Focus on worst-case D 6 Numbers indicate transistor sizing with minimum size equal to 1 F 2 A 1 D 2 2 B C Transistor Sizing

DD V DD 1 1 B 4 2 A A B 4 C F 2 C L D 2 B F 2 2 A 1 D A 2 2 B C Here it is assumed that R = R p n Design for Worst Case V Additional geometry changes which compensate for the worst case path

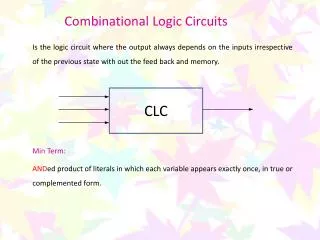

Problems with Complementary CMOS • Gate with N inputs requires 2N transistors • other circuit styles use N+1 transistors • tp deteriorates with high fan-in • increases total capacitance • series connected transistors slows down gate • fan-out loads down gate • 1 fan-out = 2 gate capacitors (PMOS and NMOS)

V DD Fan-Out : Number of Gates Connected A C D B 2 Gate Capacitances per Fan-Out A B FanIn: Quadratic Term due to: C 1. Resistance Increasing 2. Capacitance Increasing D (t ) pHL 2 t = a FI a + + FI a FO p 1 2 3 Influence of Fan-In and Fan-Out on Delay

4.0 t pHL 3.0 ) c e 2.0 t s quadratic p n ( p t 1.0 t pLH linear 0.0 1 3 5 7 9 fan-in tp as a Function of Fan-In Gate: NAND fan-out = 1 AVOID LARGE FAN-IN GATES! (Typically than FI < 4)

Out MN In C N L M 1 > M 2 > M 3 > MN C 3 In M 3 3 Distributed RC-line C M 2 In 2 2 C In M 1 1 1 Fast Complex Gate - Design Techniques • Progressive Sizing: As long as Fan-out Capacitance dominates Example 4.3: no sizing: tpHL = 1.1 nsec with sizing: tpHL = 0.81 nsec Can Reduce Delay by more than 30%!

critical path critical path C C L In L M 3 In M 1 3 1 C C 2 In M 2 M 2 2 In 2 2 C C In M 1 1 In M 3 3 1 3 (a) (b) Fast Complex Gate - Design Techniques • Transistor Ordering

Fast Complex Gate - Design Techniques • Improved Logic Design

Fast Complex Gate - Design Techniques • Buffering: • Isolate Fan-in from Fan-out C C L L Read Example 4.5

V V V DD DD DD Resistive Depletion PMOS Load V < 0 R Load Load T L V SS F F F In In In 1 1 1 In In In PDN PDN PDN 2 2 2 In In In 3 3 3 V V V SS SS SS (a) resistive load (b) depletion load NMOS (c) pseudo-NMOS Ratioed Logic Goal: to reduce the number of devices over complementary CMOS

V DD • N transistors + Load Resistive • V = V OH DD Load R L R • V = DN OL VDD R + R F DN L In 1 • Asymmetrical response In PDN 2 In • Static power consumption 3 = 0.69 R C • t pLH L L V SS Ratioed Logic

V V DD DD Depletion PMOS V < 0 Load Load T V SS F F In In 1 1 In In PDN PDN 2 2 In In 3 3 V V SS SS depletion load NMOS pseudo-NMOS Active Loads

Pseudo-NMOS NAND Gate VDD Out GND