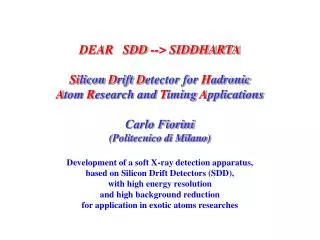

DEAR SDD --> SIDDHARTA

300 likes | 500 Views

DEAR SDD --> SIDDHARTA Si licon D rift D etector for H adronic A tom R esearch and T iming A pplications Carlo Fiorini (Politecnico di Milano) Development of a soft X-ray detection apparatus, based on Silicon Drift Detectors (SDD), with high energy resolution

DEAR SDD --> SIDDHARTA

E N D

Presentation Transcript

DEAR SDD --> SIDDHARTA Silicon Drift Detector for Hadronic Atom Research and Timing Applications Carlo Fiorini (Politecnico di Milano) Development of a soft X-ray detection apparatus, based on Silicon Drift Detectors (SDD), with high energy resolution and high background reduction for application in exotic atoms researches

Exotic atom e.m. position of K line (keV) (eV) (eV) Required precision (eV) (eV) hydrogen 6.46 160 200 ~ 5 ~ 10 deuterium 7.81 500 800 ~ 25 ~ 100 Experimental requirements

The classical PIN diode detector The anode capacitance is proportional to the detector active area

The Semiconductor Drift Detector The electrons are collected by the small anode, characterised by a low output capacitance. Anode Advantages:very high energy resolution at fast shaping times, due to the small anode capacitance, independent of the active area of the detector

The Silicon Drift Detector with on-chip JFET • JFET integrated on the detector • capacitive ‘matching’: Cgate = Cdetector • minimization of the parasitic capacitances • reduction of the microphonic noise • simple solution for the connection detector-electronics in monolithic arrays • of several units

The integrated JFET Detector produced at the MPI Halbleiterlabor, Munich, Germany

Silicon Drift Detector performances Quantum efficiency of a 300 mm thick SDD 55Fe spectrum measured with a SDD (5 mm2) at –10°C with 0.5 ms shaping time

Silicon Drift Detector Droplet or SD3 T=-30°C a τsh=1µs Canode= 50 fF (vs. 100fF conventional SDD)

SDD PIN Si(Li) 150 K 5.9 keV line 800 700 PIN Tsh=20us 600 500 FWHM (eV) 400 300 Si(Li) Tsh=20us 200 SDD Tsh=1us 100 0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 A (cm-2) Spectroscopic resolution: detector comparison - 1

Spectroscopic resolution: detector comparison - 2 FWHMmeas of monoenergetic emission line 5.9 keV 1cm2detector at 150 K SDD FWHM=140eVtshap =1ms Si(Li) FWHM=180eVtshap =15ms PIN diode FWHM=750eVtshap =20ms CCD FWHM=140eVtframe=1s

Measure of the line shift – ideal case * The case: kaonic hydrogen, 200 cm2 detection systemFor 6000 events (~50 pb-1 ) Estimated peak position 6.3 keV, line width about 245 eV, peak shift about 160 eVDetection system based on SDDs * No background contribution considered

IK IA hn hn t IA tdr max t Timing with the anode signal

Timing resolution with SDD A=0.1cm2 Tdrift = 70ns A=0.5cm2Tdrift =350ns A= 1cm2Tdrift =700ns With: r= 2kW/cm H = 450mm

Kaontrigger Concidencewindows tdr max Detectedpulses Consideredpulses Kaon trigger X-ray pulse Background pulse Triggered acquisition

Background reduction with triggered acquisition r =number of detected kaons per detected X-ray = 103Br=background rate = 103 events/s Tw=sinchronization window Tw = r xt drift max = 103x 1 ms = 1ms B = Brx Tw = 103 s-1x 10-3 s = 1 S/B = 1/1

Signal/Background with CCD ·Actual value of the S/B ratio measured with DEAR atDANEusing CCDsS/B 1/100 in kaonic hydrogen expected: S/B 1/500 in kaonic deuterium

IK IA hn hn t IK t IA tdr max t Timing with the prompt signal from the backplane Estimated time resolution: about 300 ns

Monolithic array of Silicon Drift Detectors Pixel area = 5 mm2 Total array area = 95 mm2

Pb plate Ti foil Zr foil X-ray lines BTF e+/e - beam S1 S2 scintillators Pb shielding e+, e –g shower SDD X-ray detector (4 chips prototype) DEAR test setup (SDD) at the BTF

Operations: The first stage of the project of the new detector deals with the characterization of the SDD performances. The characterization concerns the finalization of trigger efficiency and energy resolution, as a function of background environment and time window. This information will fix also the dimension of the single cell. These measurements are planned to be performed with a prototype device. The answers coming from these tests will be used for the construction of the final detector array and associated electronics with optimal characteristics.

Beam conditions at BTF: Energy: varying between 50 ÷ 750 MeV Intensity: varying between 1÷ 103e+/e- s-1 (preference is for positrons) tbunch : 10 ns; bunch frequency: 1 ÷ 49 Hz Gate window 0.1 – 1 ms BTF run period required: 2-4 weeks in the period June 2003 - October 2003

The detector: 1 cm2 SDD prototype Front-side: field strips, JFET Back-side: entrance window • 65 rings, 1 cm2 area • 280mm high-resistivity + 12mm epi-layer detector presently under test at Politecnico di Milano

Preliminary measurements Leakage current ~ 3 nA @ room T Voltage divider threshold voltage ~ -50V for 8 rings ( 65 rings bias should be feasible with ~ - 400V)