TESTING 4-BIT-ADDER BY COUNTER AND WALKING ONES

560 likes | 791 Views

TESTING 4-BIT-ADDER BY COUNTER AND WALKING ONES. GROUP MEMBERS: DIEU-NHI LE (4-Bit-Adder) STEPHEN LAM (Shift Register) BAO DOAN (Counter) CHAU HOANG (Counter). SPECIFICATIONS. Timing: Speed: Power: Shift Register Adder: P=20.1mW Counter Adder: P=20.5mW Total area:

TESTING 4-BIT-ADDER BY COUNTER AND WALKING ONES

E N D

Presentation Transcript

TESTING 4-BIT-ADDER BY COUNTER AND WALKING ONES GROUP MEMBERS: DIEU-NHI LE (4-Bit-Adder) STEPHEN LAM (Shift Register) BAO DOAN (Counter) CHAU HOANG (Counter)

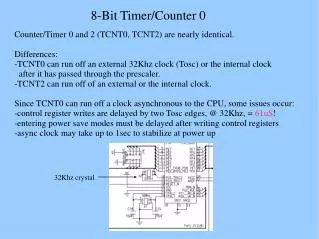

SPECIFICATIONS • Timing: • Speed: • Power: Shift Register Adder: P=20.1mW Counter Adder: P=20.5mW • Total area: Shift Register Adder: A=0.13um^2 Counter Adder: A=0.076um^2

4-BIT-ADDER - Testing 1-Bit, layout. • Testing 4-Bit, layout. • Verify the logic using Verilog.

TRUTH TABLE FOR 7474 D FLIP-PLOP 0 = low 1 = high X = irrelevant ↑ = low – to – high transition of the clock pulse

0100 1110 1100 1101 0011 1000 1001 1010 1111 0110 0101 0111 0010 1011 0001 0000 4-BIT BINARY COUNTER • A four bit binary counter we have designed in this project counts down and with every clock input moves up to the next higher state. It was designed using D type flip-flops. It has a SET signal which is setting when it is equal to 1.A CLEAR signal sets the counter back to 0.