การทดลองที่ 5 วงจรนับ (Counter)

การทดลองที่ 5 วงจรนับ (Counter). โดย รศ . ณรงค์ บวบทอง. หัวข้อ. 1. บทนำ. 2. วงจรนับ เลขไบ นารี ขนาด 2 บิต. 3. วงจรนับสิบ. 4. วงจรหารความถี่. บทนำ. 1. วงจรนับ. 2. วงจรหารความถี่. วงจรนับ. CLK. Q0. Q1. Q2. Q3. วงจรหารความถี่. วงจรนับ.

การทดลองที่ 5 วงจรนับ (Counter)

E N D

Presentation Transcript

การทดลองที่ 5 วงจรนับ (Counter) โดย รศ. ณรงค์บวบทอง

หัวข้อ 1. บทนำ 2. วงจรนับเลขไบนารี ขนาด 2 บิต 3. วงจรนับสิบ 4. วงจรหารความถี่

บทนำ 1. วงจรนับ 2. วงจรหารความถี่

วงจรนับ CLK Q0 Q1 Q2 Q3

วงจรนับ วงจรนับเป็น FSM แบบหนึ่ง สัญญาณเอาท์พุทของวงจรนับได้จากสัญญาณเอาท์พุทของฟลิปฟลอปโดยตรงวงจรนับแบ่งออกได้เป็น 2 แบบคือ Synchronous Counter และ Asynchronous Counter หรือ Ripple Counter Synchronous Counterลักษณะวงจรจะเป็นตามรูปที่ 8.16 โดยสัญญาณนาฬิกาจะป้อนให้แก่ Clock ของฟลิบฟลอบทุกตัว

วงจรนับ CLK Q0 Q1 Q2 Q3

การนับเลขไบนารี 00 01 การนับเลขไบนารี ขนาด 2 บิต Text 10 11

การนับเลข BCD หรือเลขฐานสิบ 0000 0 1001 9 0001 1 1000 8 0111 7 การนับเลขบีซีดี ขนาด 1 หลัก 0010 2 0011 3 0110 6 0100 4 0101 5

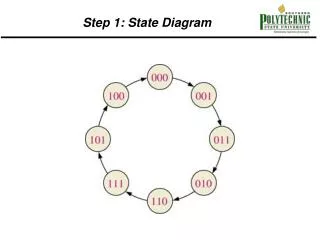

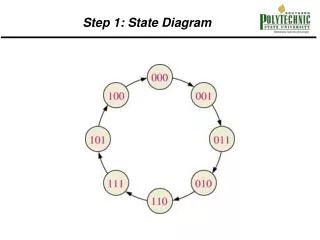

การออกแบบวงจรนับ • การออกแบบวงจรนับก็มีลำดับขั้นเหมือนกับการออกแบบ FSM คือมีขั้นตอนดังนี้ • เขียน State Diagram • เขียน State Table • หาจำนวนฟลิบฟลอบ n โดย 2n >ค่าสูงสุดที่จะนับได้ และกำหนดชนิดของฟลิปฟลอป • หาฟังก์ชั่นอินพุทของฟลิบฟลอบแต่ละตัว • เขียนวงจร

วงจรนับขึ้นแบบเลขไบนารี ขนาด 2 บิต เป็นเอาท์พุทของวงจรนับ โดย Q0 เป็นบิตที่มีนัยสำคัญต่ำ (LSB) บิต Q1 เป็นบิตที่มีนัยสำคัญสูง (MSB) CLK เป็นสัญญาณนาฬิกา

วงจรนับแบบไบนารี ขนาด 2 บิต

วงจรนับขึ้นแบบเลขไบนารี ขนาด 2บิต มีสัญญาณควบคุม เป็นเอาท์พุทของวงจรนับ โดย Q0 เป็นบิตที่มีนัยสำคัญต่ำ (LSB) บิต Q1 เป็นบิตที่มีนัยสำคัญสูง (MSB) เป็นสัญญาณควบคุมการนับ ถ้าเป็นโลจิก ‘1’ จะนับสัญญาณนาฬิกา ถ้าเป็นโลจิก ‘0’ จะหยุดนับและคงค่าสถานะเดิม เป็นสัญญาณนาฬิกา

วงจรนับขึ้นแบบเลขไบนารี ขนาด 2บิต มีสัญญาณควบคุม เขียน State Diagram แปลงจาก State Diagram เป็นตารางการทำงาน หรือ State table

วงจรนับขึ้นแบบเลขไบนารี ขนาด 2บิต มีสัญญาณควบคุม

วงจรนับขึ้นแบบเลขไบนารี ขนาด 2บิต มีสัญญาณควบคุม

การนับเลข BCD หรือเลขฐานสิบ 0000 0 1001 9 0001 1 1000 8 0111 7 การนับเลขบีซีดี ขนาด 1 หลัก 0010 2 0011 3 0110 6 0100 4 0101 5

วงจรนับขึ้นแบบเลขฐานสิบ (BCD Counter) วงจรนับจาก 0 - 9

การใช้อุปกรณ์ใน Lib. สร้างวงจรหารความถี่

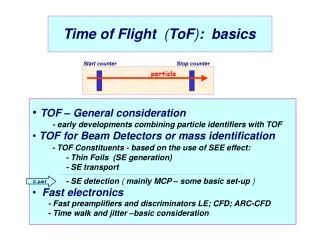

วงจรหารความถี่ The synchronous reset (R) is the highest priority input. When R is High, all other inputs are ignored; the Q outputs, terminal count (TC), and clock enable out (CEO) go to logic level zero during the Low-to-High clock transition. The Q outputs increment when the clock enable input (CE) is High during the Low-to-High clock (C) transition. The counter ignores clock transitions when CE is Low. The TC output is High when both Q outputs are High.

วงจรนับ BCD 4 หลัก พร้อมกับภาคถอดรหัสแอลอีดี 7 ส่วน

วงจรนับ BCD 4 หลัก พร้อมกับภาคถอดรหัสแอลอีดี 7 ส่วน แบบ Muxtiplex

วงจรนับเลขฐานสิบ 4 หลัก

Progress Diagram Phase 1 Phase 2 Phase 3

Block Diagram TEXT TEXT TEXT TEXT TEXT TEXT TEXT TEXT

3-D Pie Chart TEXT TEXT TEXT TEXT TEXT TEXT

Marketing Diagram Title TEXT TEXT TEXT TEXT