Layer0 Prototype Test

Layer0 Prototype Test. Abstract.

Layer0 Prototype Test

E N D

Presentation Transcript

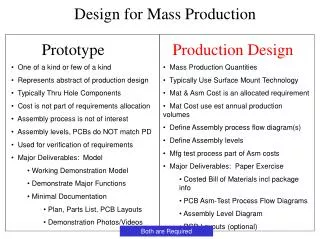

Layer0 Prototype Test Abstract We have carried out prototype test for Silicon detector for CDF experiment. Silicon Detector is important to detect B quark-jet. And Signal/Noise determines lifetime of the detector in a harsh radiation environment. Thus we carry out tested signal/noise at the prototype for Layer0 of Silicon detector. 양유철, 김동희, 조기현, 오영도, 공대정, 김민석, 김지은, 장성현, Shabeer Ahmad Mian(경북대), 유인태, 이재승, 조일성, 민선남 (성균관대), 김수봉, 이 직, 홍성철 (서울대). Yu Chul Yang(CHEP,KNU)

Hybrids Sensors Hybrids Cables Sensors Introduction Outer Barrel The new detector SVXIIb has 6 layers with 2 barrels in z, each 66cm long. Inner Layer(Layer0) Two sensors are bonded together to form a single readout unit. Fine pitch cables connect the sensors to the hybrids (2-chip). Sensors are cooled by coaxial tubes in the carbon fiber support structure. Layer 0: 12 fold Axial Layer 1: 6 fold Axial-Stereo (90o) Layer 2: 12 fold Axial-Stereo (90o) Layer 3: 18 fold Axial-Stereo (2.5o) Layer 4: 24 fold Axial-Stereo (2.5o) Layer 5: 30 fold Axial–Stereo (90o) Yu Chul Yang(CHEP,KNU)

Stave / Layout details • 2 sensors + 1 hybrid = 1 module • 3 modules per side • Modules linked by embedded bus cable and readout token passing scheme • 2 sided – axial/stereo or axial/axial • 1 Mini-Port Card /stave • Total length 66 cm • 3072 channels /stave(128*4*3*2) Yu Chul Yang(CHEP,KNU)

SVX4 Chip / Block diagram • 128-channel ADC(analog to digital converter) chip - Wilkinson type 8-bit ADC - Dead-time less Front-End : acquisition Back-End : digitization/readout - Low Power : 2.5V • Signal/Noise 30% better than SVX3 Yu Chul Yang(CHEP,KNU)

Prototype L0 & Stave in FCC • Layer0 - Silicon sensor - Cable - Hybrid(2 SVX4 chip) • Stave - Silicon sensor - Hybrid(3*4 SVX4 chip) - MPC Yu Chul Yang(CHEP,KNU)

Signal-to-Noise Ratio S/N Collected charge usually given for Minimum Ionizing Particle(MIP) But there is Noise - Capacitance - Leakage Current - Thermal Noise Radiation Damage severely degrades the S/N. Thus S/N determines lifetime of the detector in a harsh radiation environment. => We tested S/N of Layer0. Yu Chul Yang(CHEP,KNU)

Injection charge - different Pedestals How to Test • Setup - High Voltage(100V) : Silicon sensor - Low Voltage(2.5V) : SVX4 Chip - Vcal(160mV) : PMC (Injection Charge) • Test of Layer0 - Test : svxdaq (B/W, Vcal, H/V) in FCC - Make Plot : makePlot and ROOT Chip + Cable + Two Silicon Chip + Cable(broken wirebond) Yu Chul Yang(CHEP,KNU)

Linearity Test of SVX4 Chip Yu Chul Yang(CHEP,KNU)

Layer0 Prototype Test • Charge Injection Vcal = 160mV (∆ADC) 160mV * 25fF = 4.00fC = 25,000 e- Yu Chul Yang(CHEP,KNU)

Different configuration L0 1. Chip only 2. Chip + Cable 3. Chip + Cable + Two Silicon 4. Chip + Cable + One Silicon ∆ADC(Vcal:160mV) w/ 2 silicon w/ 1 silicon w/ cable Chip only Yu Chul Yang(CHEP,KNU)

Different Cable of Layer0 Keycom cable • Two layers modules with different cables. • The estimation from dnoise measurement shows similar capacit-ance (22pF for Keycom and 18.8pF for Dyconex) Dyconex cable • Dnoise = 400e- (Chip) + 40e-/pF * CpF (Cable) + 16pF * 40e-/pF (2 Sensor) Yu Chul Yang(CHEP,KNU)

Conclusion 1. Signal(ADC) Vs Vcal(V) relation is linear. 2. Different configuration test of Layer0 (Signal/Noise) => Chip+Cable+Silicon < Chip+Cable < Chip 3. Different Cable test of Layer0 (Noise) => Dyconex cable noise is smaller than Keycom. References 1) SVX4 User’s Manual, L.Christofek,…, may 22, 2003 (http://d0server1.fnal.gov/users/rapidis/svx4_man_v9.pdf) 2) The New Silicon Detector at RunⅡb, Anadi Canepa, (http://www-cdf.fnal.gov/internal/run2b/silicon/doe_poster_canepa_1.ppt) 3) The CDF runiib Silicon Detector Technical Presentation, Nicola Bacchetta (http://www-cdf.fnal.gov/upgrades/run2b/DIR_Aug02/Talks/Sil_tech_nb.pdf) Yu Chul Yang(CHEP,KNU)