Design and Simulation of a Modulo-5 3-Bit Down Counter with Load and Timeout Features

This document outlines the design of a Modulo-5 down counter, specifically a 3-bit counter that includes features such as load functionality and timeout options. The counter is designed to operate in states Q2, Q1, and Q0, and functions using a push-button clock for counting. The details include input and output declarations, truth tables, and equations governing the counter's operation. Specific attention is given to the reset functionality and how the output pins reflect the counting states on a 7-segment display.

Design and Simulation of a Modulo-5 3-Bit Down Counter with Load and Timeout Features

E N D

Presentation Transcript

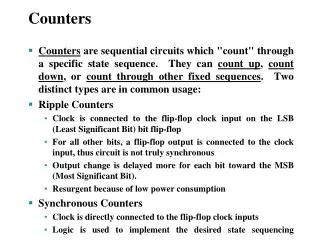

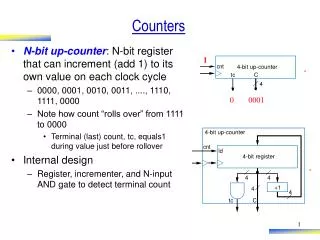

Modulo-N Counters Module M10.4 Section 7.2

Counters • Modulo-5 Counter • 3-Bit Down Counter with Load and Timeout • Modulo-N Down Counter

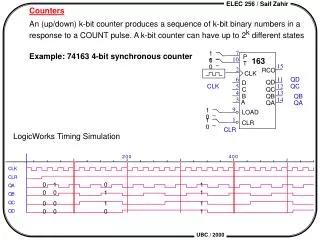

State Q2 Q1 Q0 Q2.D Q1.D Q0.D D Q Q0.D Q0 CLK !Q s0 0 0 0 0 0 1 s1 0 0 1 0 1 0 s2 0 1 0 0 1 1 s3 0 1 1 1 0 0 s4 1 0 0 0 0 0 s5 1 0 1 X X X s6 1 1 0 X X X s7 1 1 1 X X X D Q Q1.D Q1 CLK !Q D Q Q2.D Q2 CLK !Q Modulo-5 Counter

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 0 0 1 s1 0 0 1 0 1 0 s2 0 1 0 0 1 1 s3 0 1 1 1 0 0 s4 1 0 0 0 0 0 s5 1 0 1 X X X s6 1 1 0 X X X s7 1 1 1 X X X Modulo-5 Counter Q1 Q0 00 01 11 10 Q2 1 0 X X X 1 Q2.D Q2.D = Q1 & Q0

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 0 0 1 s1 0 0 1 0 1 0 s2 0 1 0 0 1 1 s3 0 1 1 1 0 0 s4 1 0 0 0 0 0 s5 1 0 1 X X X s6 1 1 0 X X X s7 1 1 1 X X X Modulo-5 Counter Q1 Q0 00 01 11 10 Q2 1 1 0 X X X 1 Q1.D Q1.D = !Q1 & Q0 # Q1 & !Q0

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 0 0 1 s1 0 0 1 0 1 0 s2 0 1 0 0 1 1 s3 0 1 1 1 0 0 s4 1 0 0 0 0 0 s5 1 0 1 X X X s6 1 1 0 X X X s7 1 1 1 X X X Note: On reset output pins are all high. Therefore, we need to include a clear input. Modulo-5 Counter Q1 Q0 00 01 11 10 Q2 1 1 0 X X X 1 Q0.D Q0.D = !Q2 & ! Q0

mod5cnt.abl MODULE Mod5Cnt TITLE ‘Modulo-5 Counter, A. Student, 7/20/02' DECLARATIONS “ INPUT PINS “ PB PIN 10; " push-button switch (clock) Clear PIN 7; " Switch 2 " OUTPUT PINS " Q2..Q0 PIN 37,36,35 ISTYPE 'reg buffer'; " LED 6..8 Q = [Q2..Q0]; " 3-bit output vector [A,B,C,D,E,F,G,DP] PIN 15,18,23,21,19,14,17,24 ISTYPE 'com'; Segments = [A,B,C,D,E,F,G]; " 7-segment LED display

mod5cnt.abl (cont’d) EQUATIONS Q.c = PB; Q0.d = !Clear & !Q2 & !Q0; Q1.d = !Clear & !Q1 & Q0 # !Clear & Q1 & !Q0; Q2.d = !Clear & Q1 & Q0; DP = PB; " decimal point @radix 16; truth_table ( Q -> Segments ) " 7-segment display … Note !Clear

mod5cnt.abl (cont’d) @radix 16; truth_table ( Q -> Segments ) " 7-segment display 0 -> 7E; 1 -> 30; 2 -> 6D; 3 -> 79; 4 -> 33; 5 -> 5B; 6 -> 5F; 7 -> 70;

mod5cnt.abl (cont’d) test_vectors([PB,Clear] -> Q) [.c.,1] -> 0; [.c.,0] -> 1; [.c.,0] -> 2; [.c.,0] -> 3; [.c.,0] -> 4; [.c.,0] -> 0; [.c.,0] -> 1; [.c.,0] -> 2; [.c.,0] -> 3; [.c.,0] -> 4; [.c.,0] -> 0; [.c.,0] -> 1; [.c.,0] -> 2; END

Simulation File, mod5cnt.si CUPL Simulation File

Note: first test vector clears output Back to LLL after 5 states CUPL Simulation File mod5cnt.si

CUPL Simulation Output File

Counters • Modulo-5 Counter • 3-Bit Down Counter with Load and Timeout • Modulo-N Down Counter

State Q2 Q1 Q0 Q2.D Q1.D Q0.D D Q Q0.D Q0 CLK !Q s0 0 0 0 1 1 1 s1 0 0 1 0 0 0 s2 0 1 0 0 0 1 s3 0 1 1 0 1 0 s4 1 0 0 0 1 1 s5 1 0 1 1 0 0 s6 1 1 0 1 0 1 s7 1 1 1 1 1 0 D Q Q1.D Q1 CLK !Q D Q Q2.D Q2 CLK !Q 3-Bit Down Counter

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 1 1 1 s1 0 0 1 0 0 0 s2 0 1 0 0 0 1 s3 0 1 1 0 1 0 s4 1 0 0 0 1 1 s5 1 0 1 1 0 0 s6 1 1 0 1 0 1 s7 1 1 1 1 1 0 3-Bit Down Counter Q1 Q0 00 01 11 10 Q2 1 0 1 1 1 1 Q2.D Q2.D = !Q2 & !Q1 & !Q0 # Q2 & Q1 # Q2 & Q0

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 1 1 1 s1 0 0 1 0 0 0 s2 0 1 0 0 0 1 s3 0 1 1 0 1 0 s4 1 0 0 0 1 1 s5 1 0 1 1 0 0 s6 1 1 0 1 0 1 s7 1 1 1 1 1 0 3-Bit Down Counter Q1 Q0 00 01 11 10 Q2 1 1 0 1 1 1 Q1.D Q1.D = !Q1 & !Q0 # Q1 & Q0

State Q2 Q1 Q0 Q2.D Q1.D Q0.D s0 0 0 0 1 1 1 s1 0 0 1 0 0 0 s2 0 1 0 0 0 1 s3 0 1 1 0 1 0 s4 1 0 0 0 1 1 s5 1 0 1 1 0 0 s6 1 1 0 1 0 1 s7 1 1 1 1 1 0 3-Bit Down Counter Q1 Q0 00 01 11 10 Q2 1 1 0 1 1 1 Q0.D Q0.D = ! Q0

timeout = 1 when [q0..2] = [0,0,0] dncnt3ld.abl MODULE DnCnt3LD TITLE '3-bit Down Counter with Clear and Load' DECLARATIONS " INPUT PINS " PB PIN 10; " push-button switch (clock) Clear PIN 7; " Switch 2 Load PIN 11; " Switch 3 X2..X0 PIN 71,66,70; " Switch 6..8 Data = [X2..X0]; " 3-bit input vector " OUTPUT PINS " LED1..LED2 PIN 44,43 ISTYPE 'com'; " LED 1..2 timeout PIN 41 ISTYPE 'com'; " LED 3 Q2..Q0 PIN 37,36,35 ISTYPE 'reg buffer'; " LED 6..8 Q = [Q2..Q0]; " 3-bit output vector [A,B,C,D,E,F,G,DP] PIN 15,18,23,21,19,14,17,24 ISTYPE 'com'; Segments = [A,B,C,D,E,F,G]; " 7-segment LED display If load = 1, Load Data to [q0..2]

dncnt3ld.abl (cont’d) EQUATIONS LED1 = Clear; LED2 = Load; Q.c = PB; WHEN Clear THEN Q.d = 0; ELSE { WHEN Load THEN Q.d = Data; ELSE { Q2.d = !Clear & !Q2 & !Q1 & !Q0 # !Clear & Q2 & Q1 # !Clear & Q2 & Q0; Q1.d = !Clear & !Q1 & !Q0 # !Clear & Q1 & Q0; Q0.d = !Clear & !Q0; } } timeout = !Q0 & !Q1 & !Q2; …

Simulation File, dncnt3ld.si CUPL Simulation File

ORDER: clock,%2,clear,load,%3,I2..0,%3,q0,%2,q1,%2,q2,%2,timeout; VECTORS: C10 XXX LLL H /* clear counter */ C00 XXX HHH L C00 XXX LHH L C00 XXX HLH L C00 XXX LLH L C00 XXX HHL L C01 101 HLH L /* load 101 into counter */ C00 XXX LLH L C00 XXX HHL L C00 XXX LHL L C00 XXX HLL L C00 XXX LLL H /* timeout */ C00 XXX HHH L C00 XXX LHH L C00 XXX HLH L C00 XXX LLH L C00 XXX HHL L C00 XXX LHL L C00 XXX HLL L C00 XXX LLL H /* timeout */ C00 XXX HHH L CUPL Simulation File dncnt3ld.si

CUPL Simulation Output File

Counters • Modulo-5 Counter • 3-Bit Down Counter with Load and Timeout • Modulo-N Down Counter

3-Bit Down Counter with Load and Timeout ______________ | dncnt3ld | clock x---|1 20|---x Vcc clear x---|2 19|---x q0 load x---|3 18|---x q1 I0 x---|4 17|---x q2 I1 x---|5 16|---x timeout I2 x---|6 15|---x x---|7 14|---x x---|8 13|---x x---|9 12|---x GND x---|10 11|---x |______________| To make a Modulo-5 counter, connect [I2..0] to 100 and connect timeout to load.

CUPL Simulation Output File