DIGITAL DESIGN INLEDNING

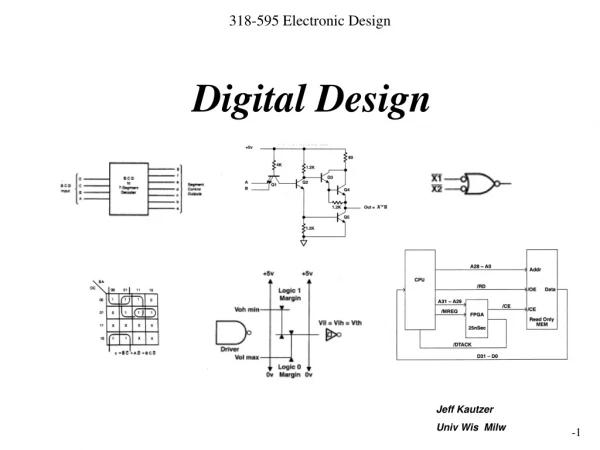

DIGITAL DESIGN INLEDNING. Allmänt och kursens hemsidor Analogt och digitalt Booleska variabler Binära tal Positiv och negativ logik (Aktiv hög och låg logik) Digitalteknikens struktur (Abstraktionsnivåer) Digitalt telefonsystem (som exempel) Klassificering av integrerade kretsar.

DIGITAL DESIGN INLEDNING

E N D

Presentation Transcript

DIGITAL DESIGNINLEDNING Allmänt och kursens hemsidor Analogt och digitalt Booleska variabler Binära tal Positiv och negativ logik (Aktiv hög och låg logik) Digitalteknikens struktur (Abstraktionsnivåer) Digitalt telefonsystem (som exempel) Klassificering av integrerade kretsar

INLEDNING Numeriska system = talsystem Decimala, binära, oktala och hexadecimala tal Addition och subtraktion Tvåkomplementmetoden Grindar och Logisk Algebra Logisk (boolesk) algebra Grindar med logiska funktioner: NOT, AND, OR etc Räkneregler Dualitet XOR

KOMBINATORISKA KRETSAR Kombinatorisk kretssyntes Minimering med Karnaughdiagram ______ Mintermer – Inne i 1-omr – Minimal SoP-form (disjunktiv) – Minimalt AND-OR-nät – Minimalt NAND_NAND-nät Maxtermer – Utanför 0-omr – Minimal PoS-form (konjunktiv) – Minimalt OR-AND-nät – Minimalt NOR-NOR-nät Ofullständigt specificerade funktioner – Don´t care Grinddelning

KOMBINATORISKA KRETSAR Kombinatorisk kretssyntes Minimering med Karnaughdiagram ______ Mintermer – Inne i 1-omr – Minimal SoP-form (disjunktiv) – Minimalt AND-OR-nät – Minimalt NAND_NAND-nät Maxtermer – Utanför 0-omr – Minimal PoS-form (konjunktiv) – Minimalt OR-AND-nät – Minimalt NOR-NOR-nät Ofullständigt specificerade funktioner – don´t care Grinddelning

KOMBINATORISKA KRETSAR Adderare Databussar mm Simulering av kombinatoriska nät (PSPICE)

INLEDNING och KOMBINATORISKA KRETSAR Numeriska och alfanumeriska koder Jämförare (Komparatorer) Multiplexer, Demultiplexer och Avkodare Busskretsar Open collector (open drain) Three-state-kretsar Transmissionsgrindar

KOMBINATORISKA KRETSAR Aritmetisk Logisk EnhetDatorns byggblockParitetskrets Grindnät i PLD (Programable Logic Device) Faktorisering Hasard och kapplöpning

INTRODUKTION AV VHDL FÖRATT REALISERA KOMBINATORISK KRETS I PLD Det hårdvarubeskrivande språket VHDLVHDL med WARP

SEKVENSKRETSAR Generella sekvenskretsar typ Moore typ Mealy Tillståndskodning Något om tillståndsminimering Något om räknare med D- och T-vippor

SEKVENSKRETSAR Räknare modulo-begreppet maximal klockfrekvens Räknare med D- och T-vippor Register och skiftregister Latchar: SR-, klockad SR-, D-latch Vippor: (pulstriggad och) flanktriggad D-vippan uppbyggd med transmissionsgrindar och inverterare

HALVLEDARMINNEN Minnesmodell Läsminnen: ROM, PROM, EPROM, EEPROM, FLASHMINNEN Skriv/Läs-minnen Statiska RWM (SRAM) Dynamiska RWM (DRAM) D/A- och A/D-OMVANDLAREFundamental OPTOELEKTRONIK