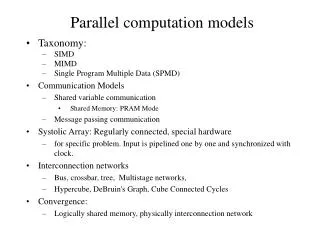

Parallel computation models

Parallel computation models. Taxonomy of network architecture: SIMD MIMD Single Program Multiple Data (SPMD) Communication Models Shared variable communication Shared Memory: PRAM Mode Message passing communication Systolic Array: Regularly connected, special hardware

Parallel computation models

E N D

Presentation Transcript

Parallel computation models • Taxonomy of network architecture: • SIMD • MIMD • Single Program Multiple Data (SPMD) • Communication Models • Shared variable communication • Shared Memory: PRAM Mode • Message passing communication • Systolic Array: Regularly connected, special hardware • for specific problem. Input is pipelined one by one and synchronized with clock. • Interconnection networks • Bus, crossbar, tree, Multistage networks, • Hypercube, DeBruin's Graph, Cube Connected Cycles • Convergence: • Logically shared memory, physically interconnection network

Mémoire Globale (Shared – Memory) P1 P2 Pp Modèle PRAM • Une extension simple du modèle classique RAM (Random Access Memory) pour prendre en compte la multiplicité de processeurs • Propriétés • p Processeurs ayant chacun une mémoire local (non accessible aux processeurs) • Une Mémoire Globale (Shared-Memory) partagée par tous les processeurs • Chaque processeur a un indexe (une identité) i (0 i p-1 qui peut être utilisé dans les comparaisons logiques ou les calculs d'adresses

Modèle PRAM Deux modes d'opération du modèle PRAM : • Synchrone • Les processeurs évoluent de manière synchronisée sous le contrôle d'une horloge commune. A chaque étape (unité de temps), les processeurs actifs exécutent la même instruction sur des données (déterminées selon les indexes des processeurs) FA chaque étape, certains processeurs sont inactifs FCe mode est adapté aux architecture de type SIMD, MIMD • Asynchrone • Chaque processeur évolue sous le contrôle d'une horloge locale. Le programmeur doit inclure des points de synchronisation quand nécessaire pour coordonner les activités des processeurs. FPlutôt adapté aux architectures MIMD

Modèle PRAM Exemple d'opération en MODE SYNCHRONE On exécute en mode synchrone sur une machine parallèle à 4 processeurs, l'instruction suivante : Algorithme : Processeur i Input : (1) A, B (2) i, identité du processeur Output : (1) C Begin If ( B==0) C = A Else C = A/B End

Initial Processeur 0 Processeur 1 Processeur 2 Processeur 3 A : 5 B : 0 C : 0 A : 4 B : 2 C : 0 A : 2 B : 1 C : 0 A : 7 B : 0 C : 0 Etape 1 Processeur 0 Processeur 1 Processeur 2 Processeur 3 A : 5 B : 0 C : 5 (Actif, B=0) A : 4 B : 2 C : 0 (Inactif, B0) A : 2 B : 1 C : 0 (Inactif, B0) A : 7 B : 0 C : 7 (Actif, B=0) Etape 2 Processeur 0 Processeur 1 Processeur 2 Processeur 3 A : 5 B : 0 C : 5 (Inactif, B=0) A : 4 B : 2 C : 2 (Actif, B0) A : 2 B : 1 C : 2 (Actif, B0) A : 7 B : 0 C : 7 (Inactif, B=0) Modèle PRAM

Modèle PRAM Quatre variantes du Modèle PRAM, selon le type d'accès simultané à une même adresse mémoire ou un bloc de mémoire • EREW : Exclusive - Read, Exclusive -Write • Les accès simultanés ( en lecture ou écriture) à une adresse mémoires sont interdits • CREW : Concurrent – Read, Exclusive – Write • Accès simultanés autorisés en lecture • Accès exclusif en écriture (une seule écriture à la fois à la même adresse) • CRCW : Concurrent – Read, Concurrent – Write • Accès simultanés en lecture • Accès simultanés en écriture F Problèmes d'écritures concurrentes F Qu'est ce qu'on écrit dans une adresse mémoire en cas d'écritures concurrentes? • ERCW : Exclusive Read – Concurrent Write

Modèle PRAM • Résolution des problèmes d'écritures concurrentes dans le modèle CRCW. Soit un ensemble de m processeurs souhaitant écrire une valeur dans une variable X, on peut distinguer 4 solutions : • Common CRCW : les écritures concurrentes sont autorisées si les valeurs écrites par les m processeurs sont égales. • SUM CRCW : la somme des valeurs est écrite dans X • Random CRCW : un processeur est choisi au hasard et autorisé à eécrire sa valeur dans X. Les autres écritures échouent (terminent sans écrire) • Priority CRCW : Une priorité est associée à chaque processeur. Le processeur de plus forte priorité est autorisé à écrire X. Les autres écritures échouent (terminent sans écrire) • Exemple : Soit P1 (50 X) , P2 (60 X), P3 (70 X) demandant des écritures simultanées sur une variable X • Common CRCW ou ERCW : échec • SUM CRCW ou ERCW : (180 X) • Random CRCW ou ERCW ( X), {50, 60, 70} …..

Modèle PRAM • Le modèle PRAM nécessite des instructions spéciales pour lire et écrire en mémoire globale • Global read (X, x) • Global write (Y, y)

Modèle PRAMExemple de Calucul (1) • Produit Matrice Vecteur Y = AX • A est une matrice n x n, X un vecteur de taille n • p processeurs opérant en mode asynchrone, pn et r = n/p • Principe de la solution • Partitionner les données en blocs. Chaque processeur calcule des résultats partiels sur une partition • Combiner les résultats partiels • Comment partitionner le calcul de Y = AX? Deux solutions : • Solution 1 : La matrice A est découpée horizontalement en p blocs Ai (sous matrices) de r lignes • Solution 2 : La matrice A est découpée verticalement en p blocs Ai (sous matrices de r colonnes) et le vecteur X est découpé en blocs de r lignes

A1 A2 …. Ap A11, A12, …, A1n A21, A22, …, A2n …. An1, An2, , Ann r lignes = A = r lignes Modèle PRAMExemple de Calucul (1) Solution 1 : Y = AX • Partition de A • Chaque Ai est une matrice r x n • Chaque processus Pi : • lit de la mémoire globale les Ai et X • calcule le produit Z = Ai X • écrit les valeurs de Z sur les composants correspondants de Y en mémoire globale

Modèle PRAMExemple de Calucul (1) Solution 1 : Y = AX • Algorithme exécuté par le processeur Pi Input Output Begin End (Faire en TD)

Modèle PRAMExemple de Calucul (1) Solution 1 : Y = AX • Analyse de la complexité • Les p processeurs lisent la valeur de X en même temps • Chaque processeur écrit dans une partie spécifique de Y, pas d'écritures concurrentes (Même si plusieurs écritures simultanées dans différentes sous blocs de Y) • O(n2/p) nombres sont transférés de la mémoire globale vers chaque processeur • O(n2/p) calculs sont nécessaires pour déterminer le produit partiel Z = Ai X F Exécution sur une architecture CREW F Pas de synchronisation des processeurs

Xp X1 A11, A12, …, A1n A21, A22, …, A2n …. An1, An2, , Ann x1,x2,…, xn A1,A2, …Ap X = Y= AX = Modèle PRAMExemple de Calucul (1) Solution 2 : Y = AX • Découper A verticalement en blocs de r colonnes A = ( A1, A2, …, Ap) , Ai est une sous matrice n x r • Découper X horizontalement en sous vecteurs de r lignes X est découpé en X1, X2, … Xp • Le processeur Pi lit les blocs Ai, Xi et calcule le produit Zi = Ai Xi r colonnes r colonnes

Modèle PRAMExemple de Calucul (1) Solution 2 : Y = AX • Solution en deux phases : • Phase 1 Les p processeurs calculent les résultats partiels Z1 =A1X1, Z2 = A2 X2, …, Zp = ApXp • Phase 2 : Calculer Y=AX = Z1 + Z2 + …, Zp F Nécessite une synchronisation en fin de phase 1. Toutes les valeurs Zi doivent être disponible avant le début de la phase 2

Modèle PRAMExemple de Calucul (1) Solution 2 : Y = AX • Algorithme (Faire en TD)

Modèle PRAMExemple de Calucul (2) Somme de n entiers sur une machine PRAM • Soit A un tableau de n éléments qui stocke les n entiers en mémoire globale. Construire un arbre binaire pour calculer la somme. (Voir cours, ceci a déjà été traité en classe)

Modèle PRAMExemple de Calucul (3) Produit de deux matrices C[Cij] = A[Aij] B[Bij] • L'élément Cij est calculé par l'expression Cij = l Ail * Blj Si on dispose de n3 processeurs dénommés par Pi,j,l (1 i,j,l n) Chaque valeur est calculé par l'ensemble de processeurs Pi,j,l (1 l n) en O(logn) unités de temps.

P0,0,3 C0,0,3 = A00 * B03 + A01 * B13 + A02 * B23 + A03 * B33 P0,0,3 C0,0,3 P0,0,2 C0,0,2 C00 = C0,0,1 P0,0,1 C0,0,0 P0,0,0 C0,0,0 C0,1,0 C0,2,0 C0,3,0 Modèle PRAMExemple de Calucul (3) Produit de deux matrices C[Cij] = A[Aij] B[Bij]

Modèle PRAMExemple de Calucul (3) Produit de deux matrices C[Cij] = A[Aij] B[Bij] • Algorithme exécuté par les processeurs Pi,j,l Input : (1) les matrices n x n A et B en mémoire globale (n = 2k) (2) Les variables locales (i,j,l) indexe du processeur Output : Le produit C = AB Begin 1. calculer C'(i,j,l) = A(i,l) * B(l,j) 2. for h = 1 to log n do if ( l n/ 2h) then C'(i,j,l) = C'(i,j,2l - 1 ) + C'(i,j,2l) 3. if (l=1) then C(i,j) = C'(i,j,1) End F Lectures concurrentes de certains éléments • Par exemple les processeurs Pi,1,l, Pi,2,l, …, Pi,n,llisent l'élément A(i,l) en même temps • Nécessité d'une architecture CREW

Modèle Réseau • Prend en compte l'architecture de communication sous-jacente • Un réseau peut être vu comme un graphe G=(N,E) dans lequel : • Chaque nœud i N est un processeur • Chaque arc (i,j)E représente une communication entre les processeurs i et j (lien direct bidirectionnel entre deux processeurs) • Propriétés • Absence de mémoire partagée • Opération peut être Synchrone ou Asynchrone • Communication et synchronisation sont faites par échanges de messages • Send (X,i) envoie le contenu de X a processeur i • Receive(Y,j) l'éxecution du processeur appelan est suspendue jusqu'à la reception d'une valeur qui est écrite dans Y (variable locale)

Réseau d'interconnexion • Objectifs • Relier les processeurs entre eux • Relier les processeurs à la mémoire commune globale • Caractéristiques d'un réseau • Latence • Temps de transmission d'un message de taille nulle dans le réseau • Bande passante • Quantité d'information acheminé par unité de temps

Pn P2 P1 Réseau statique M1 M2 Mk Réseau d'interconnexion • Deux types de réseaux d'interconnexion • Réseaux Dynamiques • Réseau dont la topologie peut varier au cours de l'exécution d'un programme. Les liens entre les éléments sont établis dynamiquement. • Il est utilisé dans les architectures à mémoire partagée

ML1 ML2 MLn Réseau statique P1 P2 Pn Réseau d'interconnexion • Deux types de réseaux d'interconnexion (…) • Réseaux Statiques • Réseau dont la topologie est fixe. Elle est définie par le constructeur de la machine multiprocesseurs. • Il est utilisé dans les architectures à mémoire distribuée

Réseaux dynamiques • Trois grandes classes de réseaux dynamiques • BUS • CROSSBAR • Réseaux Multi-étages

P1 P2 Pn BUS M1 M2 Mk Réseaux dynamiques • BUS • Permet de relier un ensemble d'éléments (processeurs, mémoires, autres) entre eux • Mise en œuvre facile et simple • L'accès au bus par un éléments bloque tout autre accès • Problèmes de conflits d'accès (Contention)

Réseaux dynamiques Switch • CROSSBAR Processeurs Mémoires

Etage1 Etage2 Etage n Réseaux dynamiques • Réseaux Multi-étages Processeurs Mémoires 0 0 1 1 . . . . . . …… P-1 P-1

Réseaux statiques • Types de réseaux statiques • Réseaux (grilles totalement connectés) • Réseaux en étoile • Réseaux linéaires • Anneaux • Grilles (Mesh) • Arborescences • Hypercubes

Réseaux statiques • Réseaux complètement connectés • Chaque sommet (processeur) est directement liés aux (p-1) autres sommets • Exemple d'un réseau complètement connecté de 10 processeurs P0 P9 P1 P2 P8 P7 P3 P6 P4 P5

P1 P8 P2 P0 P3 P7 P4 P6 P5 Réseaux statiques • Réseaux Etoile • Chaque processeur Pi ( i0) est connecté à un processeur central P0

P0 P1 P2 P3 P4 P5 Réseaux statiques • Réseaux Linéaire • Composé de p processeurs P0, P2, …, Pp-1 connectés en ligne, c'est-à-dire processeur Pi est connecté Pi+1 ( i=0, … , p-2) Exemple : Un réseau linéaire de 6 processeurs

Réseaux statiques • Réseaux en Anneau • Réseau linéaire dans lequel le premier processeur (P0) est relié au dernier processeur (Pp-1) Exemple : Un anneau de 6 processeurs P0 P1 P2 P3 P4 P5

P0 P1 P2 P3 P4 P5 P6 P7 P8 P9 P10 P11 P12 P13 P14 P15 Réseaux statiques • Une grille p processeurs est une extension des réseaux linéaires à 2 ou plusieurs dimensions. • Dans une grille à 2 dimensions, le processeur Pij est relié aux processeurs Pi+1,j,Pi-1,j, Pi,j+1, Pi,j-1 (si ces valeurs existent) • Exemple : Une grille 4X4 à 16 processeurs

P0 P1 P2 P3 P4 P5 P6 P7 P8 P9 P10 P11 P12 P13 P14 P15 Réseaux statiques • TORE (Grille avec retour) est une grille dans laquelle les lignes et les colonnes sont des anneaux. • Exemple : Un tore nXn de 16 processeurs

Réseaux statiques • Arborescence : Il existe un seul chemin entre une paire de processeurs. • Dans une arborescence statique les nœuds sont des processeurs. Les arcs représentent des liens statiques (fixes) entre les processeurs Exemple : Une arborescence à 15 processeurs

Processeur Circuit de commutation Réseaux statiques • Arborescence • Dans une arborescence dynamique, comprend deux types d'éléments • les feuilles sont des processeurs • les nœuds internes sont des éléments de commutation (switches) Exemple : Une arborescence composée de 8 processeurs et 7 commutateurs

Réseaux statiques • Arborescence : Pour améliorer la performance d'une arborescence dynamique, les capacités de communication des liens sont augmentées (ou doublées) à chaque niveau (en partant des feuilles). Exemple : Une arborescence (Fat Tree) composée de 8 processeurs et 7 commutateurs

Réseaux statiques • HYPERCUBE Défini récursivement par : • Hn en connectant les nœuds (équivalents) de deux hypercubes Hn-1 • and by Le préfixe 0 est associé au premier hypercube Hn-1 et 1 à l'autre. Hn Hn-1 Hn-1

100 101 00 01 000 001 110 111 0 0 1 010 011 10 11 d = 0 d = 1 d = 2 d = 3 1100 0100 1101 0101 1001 0001 (1) 1000 0000 (0) 0110 1110 1111 0111 1010 0010 1011 0011 d = 4 Réseaux statiques • HYPERCUBE Hypercube de dimension d

Réseaux statiques • Propriétés des hypercubes • Deux processeurs i et j sont directement connectés si et seulement les représentations binaires de (leur labels) i et j diffère d'une seule position Exemple : dans un hypercube de dimension 3 : • le processeur P0 (000) est directement connecté aux processeurs P1 (001), P2 (010), P4 (100) • Le processeur P2 (010) est directement connecté aux processeurs P3 (011), P6 (110), P0 (000) • Chaque processeur d'un hypercube de dimension d est directement connecté à d processeurs • La distance de Hamming de deux processeurs s et t d'un hypercube est le nombre de positions dans lesquelles les représentations de s et t diffèrent. • Exemple : Soit s = 0011 et t = 0110, la distance de Hamming des processeurs Ps et Pt est égale Hamming(Ps,Pt) = 2

Réseaux statiques • Propriétés des hypercubes (…) • La distance de est égal au nombre de "1" dans l'expression : s t (ou exclusif de s et t) Exemple : 0011 0110 = 0101 ===> Hamming(P0011, P0110) = 2 • La distance de Hamming de deux processeurs Ps et Pt correspond à la longueur du chemin le plus court entre Ps et Pt

Critères de Performance des Réseaux statiques • Diamètre d'un réseau • La distance entre deux processeurs d'un réseau est la longueur (nombre de liens) du plus court chemins entre ces deux processeurs • Distance maximale entre deux processeurs du réseau. La distance a un impact sur le coût de communication d'un réseau F Réseaux avec petit diamètre sont plus performant en communication • Connectivité • Définit la multiplicité de chemins entre deux nœuds (processeurs) • Connectivité (arc connectivité) est défini comme le nombre minimum d'arcs qu'on peut supprimer pour diviser un réseau en deux sous-réseaux déconnectés. • Bisection • La bisection d'un réseau est le minimum de liens qu'il faut supprimer pour partitionner le réseaux en deux sous-réseaux de taille quasi égale • Coût d'un réseau • Peut être défini par le nombre liens de communications du réseau • Coût d'un réseau linéaire de p processeurs est égal à (p-1)

Critères de Performance des Réseaux statiques • Exemples de mesures de performance de réseaux de p processeurs

Mécanismes et protocoloes de routage des réseaux statiques • Routage • Mécanisme logiciel ou matériel détermine le chemin emprunté par un message pour aller d'un processeur source à un processeur cible. • Le routage effectue : • choisit un chemin pour le transfert de message • gère les conflits • assure le bon ordre des éléments du message • Catégories de routage • Routage déterministe • Routage non-déterministe

Routage déterministe • Associe un chemin unique pour transférer un message d'une source vers une destination. • Le choix ne dépend pas des informations sur l'état du réseau. F Avantage : routage optimal. Choisit souvent le chemin le plus court F Peut résulter en une répartition non uniforme de charges sur les processeurs du réseau F Peut générer une répartition non uniforme du traffic (charge) sur les différents éléments du réseau

Routage non déterministe (ou Adaptative) • Utilise des informations sur l'état du réseau (congestion, charge) pour déterminer un chemin entre une source et une destination • Détermine la présence de congestion (ou de bouchon) du réseau et essaie de les éviter • Plusieurs catégories de routage non déterministe • Glouton : dès qu'un chemin qui rapproche de la destination est libéré, il est choisi • Aléatoire : on choisit aléatoirement le prochain nœud sur le chemin vers la destination • Aboutit à une bonne répartition des charge dans le réseau • Permet une bonne résistance aux pannes

(Y) Ps Pd (X) Exemples de routage • Routage X-Y dans une grille 2D • Etablit un ordre de parcours sur les dimensions de la grille et envoie le message suivant un ordre croissant des dimensions (e.g. X puis Y) • Routage X-Y • Pour acheminer aller du processeur Ps vers le processeur P, on transmet le message suivant la dimension X jusqu'à la colonne de Pd, puis suivant la dimension Y

Exemples de routage (…) • Routage E-Cube dans Hypercube Deux proceurs Ps et Pd d'un hypercube de dimension Les représentation binaires de s et d ont d bits La distance minimum entre Ps et Pd est égale de "1" dans s d • Routage E-Cube • Ps calcule le "Ou exclusif" s d et envoie le message suivant la dimension k, où k la position du premier bit de poids faible différent de 0 • Chaque nœud ou processeur intermédiare Pi qui recoit le message suit la même procédure, c'est-à-dire Pi clacule i d et envoie suivant une dimension correspond au premier bit de poids faible différent de 0 • Répéter jusqu'à ce le message arrive au processeur Pd

Pd 100 101 110 111 000 001 Ps Pd Pd 010 011 100 100 101 101 110 110 Pd 111 111 100 000 000 101 001 001 110 111 Ps Ps 010 010 011 011 000 001 Ps 010 011 Ps : 010 101 = 111 P011 : P001 : 011 101 = 110 001 101 = 100 Envoi suivant Envoi suivant Envoi suivant Exemples de routage (…) • Routage E-Cube dans Hypercube (…) Exemple : Message de Ps Pd