Flip Flop

700 likes | 1.05k Views

Flip Flop. יהודה אפק, יוסי מטיאס אוניברסיטת תל אביב. מבוסס על הרצאות של יורם זינגר, האוניברסיטה העברית י"ם. Storage/Mem יחידה זיכרון. מערכות זיכרון – Sequential Logic. Input כניסות. Output יציאות. Combinatorial Circuit מעגל צירופי.

Flip Flop

E N D

Presentation Transcript

Flip Flop יהודה אפק, יוסי מטיאס אוניברסיטת תל אביב מבוסס על הרצאות של יורם זינגר, האוניברסיטה העברית י"ם

Storage/Mem יחידה זיכרון מערכות זיכרון – Sequential Logic Input כניסות Output יציאות Combinatorial Circuit מעגל צירופי • עד כה טיפלנו במערכות צירופיות שהינן חסרות "זיכרון" או מצב. שינוי בערכי הכניסה גורר שינוי "מיידי" (לאחר השהייה)בערכי היציאה. • כל מחשב וכן בקרים מתוכנתים (Controllers) מכילים זיכרון המשמש לשמירת נתונים ולביצוע תוכניות. • פרט למבנים כמו SDRAM,ROM וזיכרון בועות (Bubble memory), "הזיכרון" מושג ע"י שימוש במשוב (feedback) של יחידות לוגיות.

Synchronous Sequential Circuits פעולת המערכת מתבצעת ב"פיקודו" של שעון וערכי המערכת נקבעים מערכי הכניסה בנקודות זמן מסוימות שהינן תלויות שעון מצב המערכת תלוי בשעון. Asynchronous Sequential Circuits פעולות המערכת תלויות בסדר של שינוי הכניסות, מצב המערכת יכול להשתנות בכל רגע. "יציב" "מהיר" Combinatorial Circuit Memory Clock Pulses

0 1 1 0 זכרון Q 1 2 Q’

0 1 1 0 זכרון = 0 = קלט פלט פלט 1 1 קלט 0 Q 1 2 Q’ 0

L A T C H Reset O 1 R 1 Q 1 0 0 0 0 1 2 Q’ Set S S R – L a t c h

L A T C H Reset 1 0 0 R Q 1 0 1 1 0 2 Q’ 0 0 Set S S R – L a t c h

L A T C H מקודם Reset 0 1 (1) R (0) Q 1 0 (0) (1) 0 2 Q’ Set S מקודם S R – L a t c h • נניח שניתנה פקודת Set S=1, R=0 ועתה אנו "מורידים" את הכניסות (S=0, R=0). • ערכי היציאה Q’, Q "זוכרים" את פקודת ה-Set. • באותו אופן יזכרו את ה - Reset.

L A T C H Reset 1 0 R 0 Q 1 0 0 1 2 Q’ Set S S R – L a t c h • R=1, S=1 • כאשר הערכים יורדים ל – "0" (S=0, R=0) הערך של Q ו Q’ תלוי באיזה קו ישתנה ראשון RACE Condition • המצב הבא נקרא לא מוגדר.

דיאגרמת זמנים: "1" Q "0" "1" S "0" "1" R "0" טבלת אמת – מצבים: Reset State Set State Undefined (מצב אסור) • Latch איננו פונקציה בוליאנית. • ערכי היציאה תלויים בפעולת Set או Reset האחרונה. • עבור כניסות (0,0) ערך היציאה נשמר קבוע כל זמן שיש מתח.

1 0 R Q 1 0 Q’ S 1 0 1 0 SR Latch with NAND Set State Reset State Undefined Set Command Reset Command

1 0 R Q 1 0 Q’ S 1 0 1 0 SR Latch with NAND Set State Reset State Undefined Set Command Reset Command

R R 0 Q 1 1 0 CP Q’ S S 0 SR Latch מבוקר שעון: Clock Pulse S R CP Q

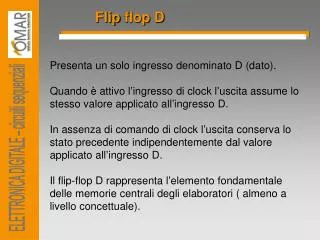

1 1 D 0 1 Q 0 1 CP 1 1 Q’ 0 0 C D Next State of Q 0 No change 1 0 Q = 0 (Reset) 1 1 Q = 1 (Set) D (data) Latch D' • Latch Dהינו יחידה שאוגרת / "זוכרת" ביט יחיד. • נמנעים ממצב לא מוגדר. • אבן בניין בסיסית של אוגרים (Registers).

D Q CP Q’ D Latch אינו מספיק !! Input כניסות Output יציאות Combinatorial Circuit מעגל צירופי מחזור שעון ארוך והמעגל יחליף את מצבו מספר פעמים !!!!

Flip - Flops • הזמן שלוקח עד שהמוצא של Latch מתייצב יכול ליצור בעיותכאשר מחברים שתי יחידות זיכרון. • המוצא אינו צריך להיות תלוי בתזמון וצריך להימנע "ממצבים מתהפכים" (JK). • פתרון צריך לדאוג שהמוצא יהיה יציב לפרק זמןמובטח. • Flip-Flop פתרון מבוסס על Latch: • שימוש בשני Latch בצורה שתבטיח שהפלט יהיה מבודד מהכניסות המשתנות: • Master-Slave Flip-Flop

M S Y S Q S Q S Q C C ג ב ר ת ע ב ד Y’ R Q’ R Q’ R Q’ C Master – Slave Flip - Flop • כאשר (master) M פעיל S (slave) אינו פעיל והינו זוכר את היציאות של M מהשלב ש – M היה סביל. C S Y Q אין השפעה!

1 נשאר 1 M S Y 01 S Q S Q S Q C C ג ב ר ת ע ב ד Y’ R Q’ R Q’ R Q’ C נעשה פעיל 0 10 01 Master – Slave Flip - Flop • כאשר M פעיל S אינו פעיל והינו זוכר את היציאות של M מהשלב ש – M היה סביל. C S Y Q אין השפעה!

S Q S Q ג ב ר ת ע ב ד C C R Q’ R Q’ D Flip Flop כן מספיק !! Input כניסות Combinatorial Circuit מעגל צירופי M S Y S Q Y’ R Q’ C

K 1 Q 3 CP Q’ 4 2 J JK Latch • "עידון" של SR Latch: • כאשר CP=0 אין שינוי מצב כמקודם. • כאשר K = 0 , J = 1 : • א) המשוב מ – Q לתוך שער 1 לא משפיע היות ו – K=0. • ב) כניסות לשער 3 הינם 0,0 Q=1Q’=0. • כאשר K=1, J=0 נקבל Q’=1 Q=0. • כאשר K=1, J=1 ?

Q=0 K=0 J=1 a ("חדש") 1 0 0 (חדש) K 1 Q 3 1 0 1 (ישן) CP ("חדש") 0 1 1 1 Q’ 4 2 J 1 (ישן) 1 JK Latch • "עידון" של SR Latch: • כאשר CP=0 אין שינוי מצב כמקודם. • כאשר K = 0 , J = 1 : • א) המשוב מ – Q לתוך שער 1 לא משפיע היות ו – K=0. • ב) כניסות לשער 3 הינם 0,0 Q=1Q’=0. • כאשר K=1, J=0 נקבל Q’=1 Q=0. • כאשר K=1, J=1 ?

Q=0 K=1 J=0 b המצב "נשמר" או Reset ("ישן") 0 1 0 0 0 K 1 Q 3 1 0 (ישן) CP 0 1 (ישן) 1 0 0 Q’ 4 2 J 0 (ישן) 1 JK Latch • "עידון" של SR Latch: • כאשר CP=0 אין שינוי מצב כמקודם. • כאשר K = 0 , J = 1 : • א) המשוב מ – Q לתוך שער 1 לא משפיע היות ו – K=0. • ב) כניסות לשער 3 הינם 0,0 Q=1Q’=0. • כאשר K=1, J=0 נקבל Q’=1 Q=0. • כאשר K=1, J=1 ?

K=1 J=1 c 1 0 0 K 1 Q 3 (1) CP 0 0 Q’ 4 2 J 1 1 (0) מצב Q מתהפך. אם 1=J=K=C לאורך זמן מצב Q יתהפך עוד ועוד. מעברים חוזרים ונשנים. JK Latch • "עידון" של SR Latch: • כאשר CP=0 אין שינוי מצב כמקודם. • כאשר K = 0 , J = 1 : • א) המשוב מ – Q לתוך שער 1 לא משפיע היות ו – K=0. • ב) כניסות לשער 3 הינם 0,0 Q=1Q’=0. • כאשר K=1, J=0 נקבל Q’=1 Q=0. • כאשר K=1, J=1 ?

טבלת אמת עבור JK: דיאגרמת זמנים: J K CP Q Q יתהפך בין 0 ל –1 הלוך ושוב כל זמן ש – cp=1

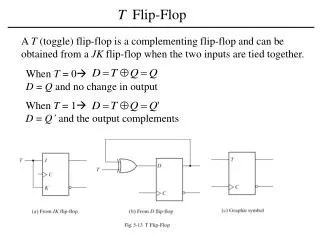

T (trigger) Latch • מתקבל ע"י חיבור J,K ב JK-Latch למקור אחד: • T = 0 J = K = 0 אין שינוי במצב • T = 1 J = K = 1 היפוך מצב • היפוך זה יחיד אם משך הזמן בו T = 1הינו "קצר"

10 Master Slave 0 1 Y1 10 1 Q (0) Q J S Q D D Latch SR Latch Y0 C 1 0 K Q’ (1) Q’ R C 1 0 0 C 01 10 JK Flip-Flop: • כאשר J = K = 1 היציאה Qהינה קבועה. • עם עליית השעון ה Master יהפוך מצב (Y התהפך). • Qישאר קבוע כל זמן שהשעון הינו "1" ו – Yישאר קבוע לאחר עליית השעון. • עם ירידת השעון הערך של Y יוכנס ל – D Latch ו – Q ישתנה.

Master Slave Y Q S Q D Q D Latch SR Latch T C Q’ Q’ R C T=1 Q(t) Q’(t+1) Q(t) Q(t) T=0 Master Slave Y Q D D D D Latch D Latch C C T (trigger) Flip-Flop D (data) Flip-Flop Q(t+1) D(t)

טבלאות המצבים: t Q(t) t+1 Q(t) שינוי של קלט שינוי של פלט JKFF SRFF DFF TFF

0 00/0 1 0 0 01/0 0 1 11/0 1 10/1 1 Finite State Machine (FSM) =Iקלט (כמקודם) =Oפלט • האוטומט פולט 1 אחרי ש"ראה" לפחות 3 1-ים מאז ה- 0 האחרון. • פלט מצוייר במצבים Moore FSM

Finite State Machine (FSM) 0/0 קלט (כמקודם) 00 1/0 0/0 0/0 01 0/0 1/0 10 פלט 1/1 11 1/1 • האוטומט פולט 1 אחרי ש"ראה" לפחות 3 1-ים מאז ה- 0 האחרון. • פלט מצוייר על הקשתות Mealy FSM

טבלת המצבים –Moore 0 00/0 1 0 01/0 1 0 11/0 1 0 10/1 1 הפלט תלוי ב – A & B

טבלת המצבים - Mealy הפלט תלוי ב - X

טבלת המצבים – Moore 0 00/0 1 0 01/0 1 11/0 1 0 10/1 1 0 AB AB I

דוגמא - Moore O Bt+1= A*I O = A*B I D Q A Q’ D Q B Q’ At+1= A*I + B * I= I(A+B) • כניסה אחת ויציאה אחת • 2FF מסוג Data 4 מצבים.

דוגמא – Mealy D Q A Q’ X Out D Q B Q’ • כניסה אחת ויציאה אחת • היציאה תלויה ב- QA, QBו- X. • 2FF מסוג Data 4 מצבים.

Moore Vs. Mealy פלט: Moore – פונקציה של המצב לבד Mealy – פונקציה של המצב והקלט אוטומט: Moore – הפלט "רשום" על המצב Mealy – הפלט "רשום" על הקשת (מעבר) שיקולים: Moore – לא תלוי ב"יציבות" הקלט (מספיק שיהיה קבוע Ts + Th) אך ידרשו FFs נוספים אם דרושה תלות היציאה בקלט. Mealy – פשוט לממוש אם יש תלות של היציאה בקלט אך נדרשת יציבות. Moore שקול ל – Mealy (ולהפך)

נוהל עיצוב • הגדר במילים את פעולת המעגל. • בנה את טבלת המצבים (אוטומט) • צמצם / מצא ייצוג קטן של אוטומט המצבים. • קבע משתנים אשר ייצגו את המצבים (בצורה וקטורית). קבע את מספר הדלגלגים והתאם אות לכל דלגלג. • בחר בסוג הדלגלג להשתמש בו. • קבל טבלאות העירור והיציאות של המעגל מטבלת המצבים. • חשב את פונקציות היציאה של המעגל ואת פונקציות הכניסה של FF (בעזרת מפות קרנו או כל שיטה אחרת) • צייר הדיאגרמה הלוגית. *

דוגמת תכנון IRobot "תקין" "תקין" "שמאלה" "ימינה" מערב מרכז "ימינה" מזרח "שמאלה" "תקין" "תקין" "שמאלה" "ימינה" "תקוע" "תקוע"

אוטומט המצבים – תיאור סמלי: מרכז תקין / שמאל תקין / ימין תקין / ימין תקוע / שמאל תקין / שמאל מזרח מערב תקוע / ימין

אוטומט המצבים: תקין : 0תקוע : 1 "ימין" : 0"שמאל" : 1 A B 00 קלט 0/0 1/0 מרכז 1/1 10 01 0/0 1/0 פלט מזרח מערב 0/1 • 3 מצבים • נזדקק ל – 2FF • 2FF יכולים "לזכור" 4 מצבים. • מצב שלא משתמשים בו ("11")

פונקציות יציאה + מצב הבא: מימוש עבורD-FF Bt A(t+1)= B’X’ = (B+X)’ At Xt Bt B(t+1) = A’X At Xt Bt Y(t) = AX’ + BX At Xt

דיאגרמה לוגית: AX’ X D Q B’X’ A C Q’ y D Q A’X B BX C Q’ מימוש עבור DFF (שעון מושמט)

Graphical Specification of FSM • How many state bits will we need?

Finite State Machine for Control 0 0 0 0 0 1 1 0 0 1 1 1 0 0 0 1 0 1 1 0 0 0 1 1 1 0 0 0 1 0 0 0 0 0 0 1 0 1 0 0 0 1 1 1 0 0 1 1 0 1 1 1 0 1 1 1

state Control signals S3 S2 S1 S0 ALUSrcA PCWrite PCWriteCond 0 0 0 0 0 1 0 fetch decode 0 0 0 1 0 0 0 0 0 1 0 1 0 0 AdrCmp load 0 0 1 1 X 0 0 WB 0 0 0 1 0 0 X 0 1 0 1 X 0 0 store 0 1 1 0 ALU 1 0 0 WBR 0 1 1 1 X 0 0 1 0 branch 1 0 0 0 1 1 0 0 1 X 1 0 jump All other combinations X 0 0 The control signals decoder We just implement the table of slide 54: Let’s look at ALUSrcA: it is “0” in states 0 and 1 and it is “1” in states 2, 6 and 8. In all other states we don’t care. let’s look at PCWrite: it is “1” in states 0 and 9. In all other states it must be “0”. And so, we’ll fill the table below and build the decoder.

opcode current state next state IR31 IR30 IR29 IR28 IR27 IR26 S3 S2 S1 S0 S3 S2 S1 S0 Fetch 0 X X X X X X 0 0 0 0 0 0 0 1 Decode 1 0 0 0 0 0 0 0 0 0 1 0 1 1 0 j lw+sw beq 1 X X X X X 0 0 0 1 0 0 1 0 R-type AdrCmp 2 Jump 9 Branch 8 X X 0 X X X 0 0 1 0 0 0 1 1 ALU 6 lw sw 0 0 1 0 0 1 0 1 X X 1 X X X Load 3 Store 5 WB 4 WBR 7 The state machine “next state calc.” logic R-type lw+sw lw sw R-type=000000, lw=100011, sw=101011, beq=000100, bne=000101, lui=001111, j=0000010, jal=000011, addi=001000

Interrupt and exception Type of event From Where ? MIPS terminology Interrupt ExternalI/O device request ------------------------------------------------------------------------------------ Invoke Operation system Internal Exception From user program ------------------------------------------------------------------------------------- Arithmetic Overflow Internal Exception ------------------------------------------------------------------------------------- Using an undefined Instruction Internal Exception -------------------------------------------------------------------------------------- Hardware malfunctions Either Exception or interrupt

Exceptions handling Exception type Exception vector address (in hex) Undefined instruction c0 00 00 00 Arithmetic Overflow c0 00 00 20 We have 2 ways to handle exceptions: Cause register or Vectored interrupts MIPS – Cause register