Flip Flop

Flip Flop. 主講人:林佳慶 http://www.cis.nctu.edu.tw/~jacklin/ jacklin@cis.nctu.edu.tw. Outline. Propagation Delay Review 循序電路 SR Latch D Flip-Flop JK Flip-Flop Example. Propagation Delay. Gate Delay. Timing Diagram. equivalent to “ Switch ”. equivalent to “ Inverter ”.

Flip Flop

E N D

Presentation Transcript

Flip Flop 主講人:林佳慶 http://www.cis.nctu.edu.tw/~jacklin/ jacklin@cis.nctu.edu.tw

Outline • Propagation Delay Review • 循序電路 • SR Latch • D Flip-Flop • JK Flip-Flop • Example

Propagation Delay Gate Delay

Timing Diagram equivalent to “Switch” equivalent to “Inverter”

Conclusion of Time Delay • The overall gate delay will determine the speed of the circuit. • The gate delay can not be displayed in the logic simulator. • In the Xilinx, the gate delay can be observed in the simulator after implementation, next to the function block of implementation.

CLK 循序電路(1/2) • 組合電路(Combinational circuit)並不會儲存之前發生過的狀態,循序電路(Sequential circuit)會根據目前的狀態來決定下一次的輸出狀態

Reset Next Next Next Next Next 0 1 2 3 4 5 Reset Reset Reset Reset Next/Reset 循序電路(2/2) • Example:計數器

SR Latch(1/4) • 由二個NOR構成的正緣觸發SR正反器 • S=1,Q設為1;R=1,Q設為0

SR Latch(2/4) • 正緣觸發的時序圖

SR Latch(3/4) • 下圖的SR正反器由二個NAND構成,具有回饋電路,不同前者的是,以負緣觸發

SR Latch(4/4) • 具有控制訊號的SR正反器

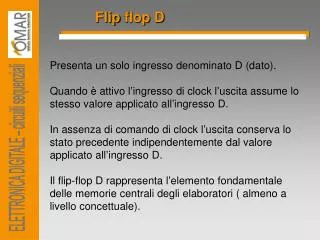

D Latch(2/2) • 負緣觸發D正反器 的時序圖

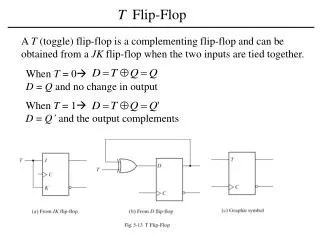

JK Filp-Flop • Master-Slave JK Flip-Flop(pulse-triggered flip-flop)

Flip-Flop Characteristic Tables 相當於將JK Flip-Flop的輸入接在一起

Q1Q0Q1+Q0+D1D0 0 0 0 1 0 1 0 1 1 0 1 0 1 0 1 1 1 1 1 1 0 0 0 0 D1 Q0 Q1 D0 DFF DFF CLK 範例:以D正反器建立二位元計數器 • 取得D正反器的Function Table • 畫出2-bit counter with D Filp-Flop的Next-State Table 00 01 10 11

範例:以D正反器建立二位元計數器 • 以觀察歸納或K-map導出D1/D0的Boolean Equation D0=~(CLK) D1=Q0 XOR Q1