Flip - Flop

Flip - Flop. Oleh: Satriyo, ST, MKom. Rangkaian Logika. Rangkaian Kombinasional rangkaian yang kondisi keluarannya (output) dipengaruhi oleh kondisi masukan (input ) Contoh: Dekoder,Mutiplekser

Flip - Flop

E N D

Presentation Transcript

Flip - Flop Oleh: Satriyo, ST, MKom

Rangkaian Logika • Rangkaian Kombinasional rangkaian yang kondisi keluarannya (output) dipengaruhi oleh kondisi masukan (input ) Contoh: Dekoder,Mutiplekser • Rangkaian Sequensial rangkaian logika yang kondisi keluarannya dipengaruhi oleh masukan dan keadaan keluaran sebelumnya atau dapat dikatakan rangkaian yang bekerja berdasarkan urutan waktu. Contoh: Flip – flop, counter

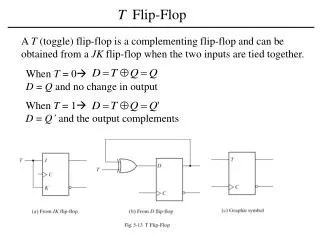

Hubungan I/o flip - flop • Set, yaitu jika suatu kondisi masukan mengakibatkan keluaran (Q) bernilai logika positif (1) saat dipicu, apapun kondisi sebelumnya. • Reset, yaitu jika suatu kondisi masukan mengakibatkan keluaran (Q) bernilai logika negatif (0) saat dipicu, apapun kondisi sebelumnya. • Tetap, yaitu jika suatu kondisi masukan mengakibatkan keluaran (Q) tidak berubah dari kondisi sebelumnya saat dipicu. • Toggle, yaitu jika suatu kondisi masukan mengakibatkan logika keluaran (Q) berkebalikan dari kondisi sebelumnya saat dipicu.

Pemicu Flip – flop(Clock) • Untuk menyerempakkan masukan • Kondisi clock yang dapat digunakan: • Tepi naik : yaitu saat perubahan sinyal clock dari logika rendah (0) ke logika tinggi. • Tepi turun : yaitu saat perubahan sinyal clock dari logika tinggi (1) ke logika rendah (0). • Logika tinggi : yaitu saat sinyal clock berada dalam logika 1. • Logika rendah : yaitu saat sinyal clock berada dalam logika 0

SR Flip - flop • Mempunyai dua masukan S dan R • Mempunyai dua keluaran Q dan Q’

SR Lacth • Aplikasi : Debouncer pada switch

Efek Bouncing pada switch • Debouncer

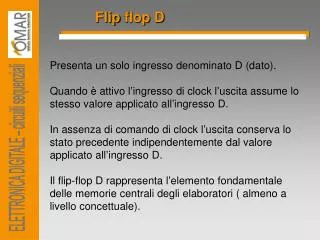

D Flip - Flop • Mempunyai dua masukan D dan C • Mempunyai dua Keluaran Q dan Q’

Latihan • Tentukan diagram waktu untuk Keluaran Q 1 2

3 4 5