Busy logic for the ALICE TPC ...

80 likes | 239 Views

Busy logic for the ALICE TPC. Anders Rossebø UiB. TPC BUSY generation. Located in the counting house Standalone PCB (19” rack mount) Input TTC L0, L1, L1 message L2r and L2a message Clock D-RORCs 216 End-of-Transfer (EoT) messages 216 Arrival-of-Header (AoH) messages (?)

Busy logic for the ALICE TPC ...

E N D

Presentation Transcript

Busy logic for the ALICE TPC ... Anders Rossebø UiB

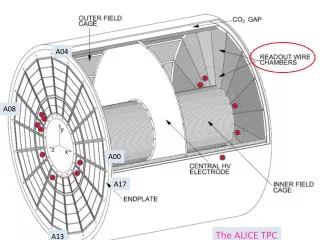

TPC BUSY generation • Located in the counting house • Standalone PCB (19” rack mount) • Input • TTC • L0, L1, L1 message • L2r and L2a message • Clock • D-RORCs • 216 End-of-Transfer (EoT) messages • 216 Arrival-of-Header (AoH) messages (?) • Ethernet (DCS) • Output • BUSY signal to CTP • Internal variables • Number of free ALTRO buffers = n_free_buffer • Number of free RCU ping-pong buffers = n_free_pp

BUSY control flow • Initialization at run start • n_free_buffer = NUMBER_OF_FEC_BUFFERS • n_free_pp = 2 • Collision ALIVE • L1, L1 message • TPC in trigger mask BUSY • L2 message • L2r ALIVE • L2a • IF(n_free_buffer > 0) ALIVE • ELSE BUSY • Decrement n_free_buffer & n_free_pp • Event fragment header @ LDC • IF((EoT == TRUE).AND. (n_free_pp > 0)) increment n_free_buffer • Event fragment has arrived in LDC • ELSE IF(EoT == TRUE) increment n_free_buffer t = 0 t = 5.5 sec t = 100 sec t = 2 msec

Busy logic Interfaces • Trigger-IF • TTC, BUSY • DCS-IF • DIM, TCP/IP, Ethernet • RORC-IF • Topology • 216 point-to-point connections (STAR topology) • Prototocol • SIMPLEX: unidirectional data transfer (event ID, fragment size), ACK Anders Rossebø, 2006

Implementation (1) Conceptual design • RJ-45 connectors for input and output • 2 FPGAs (Xilinx XC4VLX40) • DCS board uses Xilinx SelectMAP interface for programming the FPGAs • Clock from DCS board • JTAG interface • Serial communication (LVDS) • One ethernet cable for each D-RORC Logic design • firmware and ARM-software (C/linux) Inside the busy box Ethernet Anders Rossebø, 2006

Implementation (2) Connection to D-RORC • Connectors has same pinout as ethernet • Busy logic sends an acknowledge to D-RORC after receiving data • TBD in collab. with DAQ Connection to D-RORC boards RJ-45 connector pinout • Pair 3 for data to busy logic • Pair 2 for acknowledge to D-RORC • Cat-5 ethernet cable Anders Rossebø, 2006

Implementation (3) Side view • Four extra boards for RJ-45 connectors • Extra boards connected to mainboard thru 2 x 96-pin flat cable 19-inch housing Front panel • Height: 5 U (1 U = 44 mm)Width: 482,6 mm (19”)Depth: 450 mm (TBC) Anders Rossebø, 2006

Next steps • Soon (Anders will come to CERN on May 3rd) • Detailed specification of hardware/software protocol between DRORC and BUSYBOX - in collaboration with DAQ (Csaba, Wolfgang) • Specification of event fragment message - in collaboration with DAQ (Csaba, Wolfgang) • June • First board prototype • Development of firmware/software – in collaboration with DAQ (Csaba, Wolfgang)