Level-1 Trigger for SVD2

Level-1 Trigger for SVD2. Requirements Logic Overview Implementation To Do. K. Hasuko (RIKEN/RBRC) 30 April 2003. SVD2 Level-1 Trigger. Make regional matching between SVD and CDC Requirements Compensate for the absence of the CDC Z trigger Reduce trigger rate by 30% (400Hz -> 300Hz)

Level-1 Trigger for SVD2

E N D

Presentation Transcript

Level-1 Trigger for SVD2 • Requirements • Logic Overview • Implementation • To Do K. Hasuko (RIKEN/RBRC) 30 April 2003 K Hasuko - Belle Trigger Meeting

SVD2 Level-1 Trigger • Make regional matching between SVD and CDC • Requirements • Compensate for the absence of the CDC Z trigger • Reduce trigger rate by 30% (400Hz -> 300Hz) • Same output format as present • Inputs • SVD_Z (18 bits) and SVD_Rf (18 bits) from L0 on FADC • Asynchronous • Latency: 285~580ns + a • Jitter: 295ns • Pulse width: 48ns (for Tp = 300ns) • CDC_Rf (64 bits) • Asynchronous • Latency: 900~1400ns + a • Jitter: 500ns • Pulse width: 180~680ns • Outputs • #matched tracks (2-3 bits) • open (1 bit), back-to-back (1 bit) • Pulse width: 3x16MHz clocks => ~180ns K Hasuko - Belle Trigger Meeting

Timing Chart K Hasuko - Belle Trigger Meeting

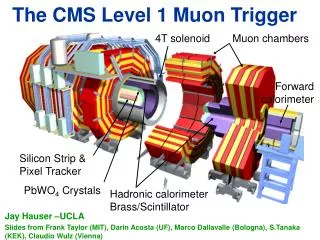

SVD L1 Trigger (L1T) Logic • SVDCDC-S (short tracks) and SVDCDC-L (full tracks);use two general-purpose trigger boards (so-called “Tanaka boards”) • Regional matching based on CDC segmentation (64 wedges) • HDL source available at http://rarfaxp.riken.go.jp/~hasuko/research/belle/svd/l1t/ K Hasuko - Belle Trigger Meeting

Components • Pipeline delays • Variable delays: 0 ~ 63 clk (0 ~ 992ns) • Using LUT shift registers • Pulse stretcher • For SVD signals • Variable length: 0 ~ 63 clk (0 ~ 992ns) • Matching logic • Check SVD-CDC matching for each CDC wedge • Make OR two SVD wedges if they match with a single CDC wedge • Enable/disable OR’s • Clustering / Track finder • Clustering algorithm • Counter • Count all the tracks (up to 64 => 2- or 3-bit format) • Event topology • Event topology algorithm to identify back-to-back or open (>135deg) • VME I/F • Write/read parameters K Hasuko - Belle Trigger Meeting

SVD-CDC Matching • Make coincidence between each CDC wedge and the SVD wedges with the same phi coverage K Hasuko - Belle Trigger Meeting

Clustering Algorithm • For position i, Look at [i-2:i+1] and cluster up to 3 contiguous hits • n (>2) contiguous hits are clustered into n-2 hits K Hasuko - Belle Trigger Meeting

Logic Implementation • Implemented with XCV600HQ240 • Resources used • IOBs: 133/166 (80%) • SLICEs: 2293/6912 (33%) • Maximum clock: 79MHz • Will be operated with 63.5MHz K Hasuko - Belle Trigger Meeting

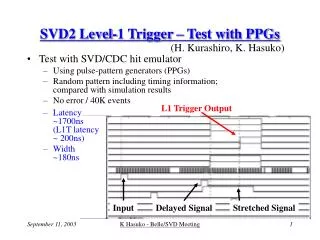

Functional/Timing Simulation • Inputs • SVD_Z = 18’b00000011000000101 @ 285ns, w=48ns • SVD_Rf = 18’b00000010100000001 @ 580ns, w=48ns • CDC = 16’h0000000100080021 @ 1400ns, w=180ns • Outputs = 8’b11010011 (#match_z = 3, #match_rphi = 2, open, back-to-back) • @ 1500ns, w=180ns K Hasuko - Belle Trigger Meeting

To Do • Check scheme • Stretched SVD signals cause accidental coincidences? • Clustering algorithm is OK? • Check functionalities • Satisfy all the requirements? • Any other options? • Optimize logic • Reasonable resource usage; route delays? • Check/list up parameters • Test whole logic with emulator (PPG) • Cosmic-ray test K Hasuko - Belle Trigger Meeting