The CMS Tracking Readout and Front End Driver Testing

150 likes | 168 Views

This article provides an overview of the CMS tracking readout system and front-end driver testing, discussing various components and operational modes. It also highlights the testing process and future plans for the system.

The CMS Tracking Readout and Front End Driver Testing

E N D

Presentation Transcript

The CMS Tracking ReadoutandFront End Driver Testing Matthew Pearson RAL Matthew Pearson

Inner Barrel + Disks End-caps 2,4 m 5.4 m OuterBarrel Inside the CMS Tracker Matthew Pearson

Tracking Parameters Pixel Detector: 3 barrel layers + 2 end cap disks 4cm, 7cm and 10cm in r 35cm, 47cm in z 2 hit acceptance up to rapidity=2.2 ~44M channels Silicon Strip Detector: 4 inner / 6 outer barrel layers + 3 inner / 9 forward end cap disks Up to rapidity=2.4 acceptance ~10M channels Channel occupancy is ~1-3% Matthew Pearson

Z view of silicon tracker Matthew Pearson

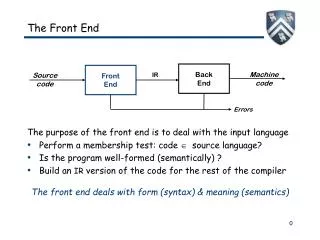

The Readout Chain in Pictures L1 trigger 40 MHz 100 kHz Highlevel trigger (computer farm) Yes/No CMS 3.2 ms buffer 1 s buffer 100 Hz 1 MB/event The Trigger and Data Acquisition System selects interesting events, and reduces the data rate so we can write to mass storage (~100MB/s). Mass Storage. Matthew Pearson

Si Strip Readout Components The APV reads out the Si strips. The Front End Controller controls the APV chips and provides them with L1 triggers and a clock. Data passed by L1 is sent to the Front End Drivers, which perform data reduction. The FED passes data to the DAQ and the High level Trigger. Matthew Pearson

Si Strip Readout Components 2 APV chip: Each APV chip reads pulse height data from 128 silicon strips. They amplify and buffer the data for 3.2ms. On a L1 trigger accept, the data is passed to… Front End Driver (FED): Each FED reads 192 APVs, digitizes signal and FPGA performs data reduction/processing. The data is transmitted at ~40MHz along an S-LINK64 to the DAQ event builder (up to ~320MB/s per FED). Matthew Pearson

Opto- Rx Zero Suppression FGPA ADC 12 12 12 12 12 12 12 12 VME 96 opticalinput channels DAQ Event Builder FPGA The Front End Driver (FED) • 96-channel final FED • Digitize and zero suppress data. • FPGA chips give flexibility. • 9U-VME modularity. • Processes 25k silicon strips. Designed by physicists and engineers at RAL and IC. Both are still involved in testing the FED. Matthew Pearson

The FED Data Processing • The FED takes analogue optical signals from the APV… • 96 10-bit ADCs • Delay FPGAs (to take into account differences in fibre length) • Front End FPGA: • Subtract strip dependant pedestal • Re-ordering of signals in strip order • Calculate and subtract the common mode noise • Zero suppress the data • Send ‘event’ to back-end FPGA and S-LINK64 • Can check if FED is working as we expect during a run • by using the spy channel -> read out raw data over VME • and compare to zero suppressed data. Matthew Pearson

FED Photo and Operational Modes • FED Modes: • Zero Suppression • Normal mode. • Used for pp and light • ion collisions. • Processed raw data • No zero suppression • or CM subtraction. • Used for heavy ion • collisions. • Raw data • As above, but no • reordering or pedestal • subtraction. • Used for testing and • calibration. Matthew Pearson

FED Status and Testing • At RAL and IC we have 2 final design FEDs • Currently in the testing process (see below) • Aim to have 2 more made this year (to distribute to • different tracker subgroups for test-beam work etc.) • Produce 10 more in 2004 (with any revisions) • Full production starts in 2005 • Testing: • Currently testing 2 FEDs at RAL and IC • Complex board will take at least 9 months. • But is ongoing in terms of firmware. • Electrical, digital and optical testing Matthew Pearson

Optical test setup ….still very much in progress! Matthew Pearson

FED test setup Matthew Pearson

Summary • The FED is on schedule and is passing all tests. • The bulk of future work will involve: • FED on-line software (design and testing) • At the moment we are organizing who does • what and when… • Verifying FPGA algorithms • Making sure FED responds well to CMS-like data. Matthew Pearson