제 5 강 캐시 기억장치 (Cache Memory)

제 5 강 캐시 기억장치 (Cache Memory). 학습 목차. 컴퓨터 본체에서 기억장치 위치 살펴보기 컴퓨터 기억장치의 계층적 구조 캐시 기억장치 원리 캐시 기억장치의 설계 다중 프로세서를 사용하는 시스템에서의 캐시 기억장치. 학습 목표. 기억장치들간의 상호 연관성에 대해 이해한다 . 캐시 기억장치의 원리에 대해서 이해한다 . 캐시 기억장치와 주기억장치 사이의 정보교환 방법에 대해 이해한다 . 캐시 기억장치의 교환 알고리즘에 대해 이해한다. 컴퓨터 기억장치의 계층적 구조.

제 5 강 캐시 기억장치 (Cache Memory)

E N D

Presentation Transcript

학습 목차 • 컴퓨터 본체에서 기억장치 위치 살펴보기 • 컴퓨터 기억장치의 계층적 구조 • 캐시 기억장치 원리 • 캐시 기억장치의 설계 • 다중 프로세서를 사용하는 시스템에서의 캐시 기억장치

학습 목표 • 기억장치들간의 상호 연관성에 대해 이해한다. • 캐시 기억장치의 원리에 대해서 이해한다. • 캐시 기억장치와 주기억장치 사이의 정보교환 방법에 대해 이해한다. • 캐시 기억장치의 교환 알고리즘에 대해 이해한다.

컴퓨터 기억장치의 계층적 구조 • 컴퓨터의 기억장치의 용량, 접근 속도, 가격의 상관관계 • 접근 속도를 감소시켜 데이터의 읽고, 쓰기 속도를 향상시키기 위해서는 고가이지만 고속의 기억장치가 필요 • 많은 양의 데이터를 저장하기 위해서 기억장치의 용량이 커져야 한다. 그러나 적정 비용을 위해서는 저가의 기억장치를 필요로 하게 된다. • 저가의 기억장치를 사용하면 기억장치의 접근속도는 그만큼 증가하게 된다. • 이 요건들의 적절한 상호 조정이 필요하며, 이를 위해서 기억장치 계층 구조가 이용된다.

캐시 기억장치 원리 • 빠른 접근 시간을 제공하는 기억장치 • 수행할 명령어나 오퍼랜드를 주기억장치로부터 가져와 저장하고 있다가 빠른 속도로 중앙처리장치에 제공

캐시 기억장치의 동작 원리 • 캐시 기억장치가 없는 시스템 • ① 중앙처리 장치의 주기억장치 접근 • ② 주기억장치로부터 명령어나 필요한 정보 획득

캐시 기억장치의 동작 원리 • 캐시 기억장치가 있는 시스템 • 중앙처리 장치가 기억장치를 참조할 필요가 있을 경우 캐시 기억장치를 먼저 조사 • 캐시 기억장치에 접근하여 그 내용을 찾았을 때 적중(hit)이라고 하고, 찾지 못하였을 경우를 실패(miss)라고 한다. • 중앙처리장치가 1000번지 워드를 필요로 하는 경우 • 캐시 기억장치를 검사하고실패(miss)하면 • 주기억장치로부터 정보를 획득하여 캐시 기억장치에 전송 • 캐시 기억장치는 정보를 다시 중앙처리장치로 전송

캐시 기억장치의 동작 원리 • 캐시 기억장치가 있는 시스템에서 중앙 처리장치가 1002번지의 워드를 필요로 하는 경우 • 캐시 기억장치 검사 • 적중(hit) • 캐시 기억장치에서 얻어진 정보를 중앙처리장치로 전송 • 주기억장치를 거치는 것보다 훨씬 빠른 속도로 정보 획득

참조의 지역성(locality of reference) • 캐시는 중앙처리장치가 수행할 명령어와 필요한 정보를 저장하고 있다가 즉시 제공함으로써 처리가 신속하게 이루어지도록 함 • 캐쉬 동작은 프로그램 내장형 컴퓨터의 특성인 기억장치 참조의 지역성(locality of reference)으로 인하여 가능 • 참조의 지역성 • 주어진 시간 동안 중앙처리장치의 기억장치 참조는 제한된 영역에서만 이루어지는 현상 • 짧은 시간 동안 중앙처리장치가 접근하는 범위는 지역적으로 제한되는 것을 의미

적중률(Hit ratio) • 캐시 기억장치 성능은 적중률(hit ratio)에 의해 측정 • 주기억장치와 캐시 기억장치 사이에서의 평균 기억장치 접근 시간 Taverage = Hhit_ratio × Tcache + (1-Hhit_ratio) × Tmain Taverage = 평균 기억장치 접근시간 Tmain = 주기억장치 접근시간 Tcache = 캐시 기억장치 접근시간 Hhit_ratio = 적중률 • 캐시의 적중률이 높아질수록 평균 기억장치 접근 시간은 캐시 액세스시간에 접근

캐시 기억장치의 설계 • 캐시 기억장치를 설계함에 있어 공통적인 목표 • 캐시 적중 시 캐시 기억장치로부터 데이터를 읽어오는 시간을 짧게 • 캐시 실패 시 주기억장치로부터 캐시 기억장치로 데이터를 읽어 오는 시간을 최소화 • 주기억장치와 캐시 기억장치 사이에 데이터의 일관성을 유지 • 캐시 기억장치를 설계할 때 고려 사항 • 캐시 기억장치의 크기(Size) • 인출방식(fetch algorithm) • 사상함수(Mapping function) • 교체 알고리즘(Replacement algorithm) • 쓰기 정책(write policy) • 블록 크기(Block size) • 캐시 기억장치의 수(Number of caches)

캐시 기억장치의 크기와 인출 방식 • 캐시 기억장치의 크기 • 용량이 커질수록 적중률은 높아지지만, 이에 따른 비용 또한 증가 • 용량과 비용간의 조정을 통해 적절한 용량과 비용이 결정 • 용량이 커질수록 주소 해독 및 정보 인출을 위한 주변 회로가 더 복잡해지기 때문에 액세스 시간이 다소 더 길어진다. • 인출방식 • 요구 인출(demand fetch) 방식 • 현재 필요한 정보만 주기억장치로부터 인출해 오는 방식 • 선인출(prefetch) 방식 • 현재 필요한 정보 외에도 앞으로 필요할 것으로 예측되는 정보도 미리 인출하는 방식 • 지역성(locality)이 높은 경우에 효과가 높지만 그렇지 못한 경우에는 인출 시간이 길어지기 때문에 효율이 떨어지게 된다.

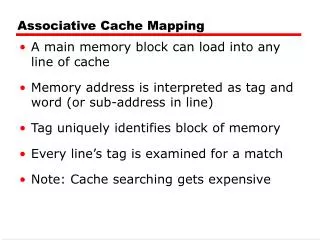

사상(mapping)함수 • 주기억장치와 캐시 기억장치 사이에서 정보를 옮기는 것 • 직접사상(direct mapping) • 연관사상(associative mapping) • 집합 연관사상(set-associative mapping)

직접사상(Direct mapping) • 주기억장치의 블록이 특정 라인에만 적재 • 캐시의 적중 여부는 그 블록이 적재 될 수 있는 라인만 검사 • 간단하고 비용이 저렴한 장점 • 주기억장치의 블록이 적재 될 수 있는 라인이 하나 밖에 없음 • 프로그램이 동일한 라인에 적재되는 두 블록들을 반복적으로 액세스하는 경우 캐시 실패율이 매우 높아진다.

직접 사상의 동작 • 중앙 처리장치가 00001번지 워드를 필요로 하는 경우

직접 사상의 동작 • 처음의 2-bits(00)는 태그, 다음 3-bits(001)는 캐시 기억장치의 주소 표시. 캐시 기억장치에서 001번지 주소를 참조. 해당 번지가 비어 있으므로 실패(miss) 주기억장치를 참조 • 주기억장치로부터 워드를 획득 • 캐시 기억장치의 해당 주소에 데이터와 태그 저장

직접 사상의 동작 • 중앙 처리장치가 00010번지 워드를 필요하는 경우

직접 사상의 동작 • 처음의 2-bits(00)는 태그를 나타내고, 다음 3-bits(010)는 캐시 기억장치의 주소를 표시. 캐시 기억장치에서 010번지 주소를 참조. 해당 번지가 비어 있으므로 실패(miss) 주기억장치를 참조 • 주기억장치로부터 워드 획득 • 캐시 기억장치의 해당 주소에 데이터와 태그 저장

직접 사상의 동작 • 중앙 처리장치가 10001번지 워드를 필요하는 경우

직접 사상의 동작 • 처음의 2-bits(10)는 태그를 표시하고, 다음 3-bits(001)는 캐시 기억장치의 주소를 표시. 캐시 기억장치에서 001번지 획득, 태그가 00으로 불일치 • 주기억장치로부터 워드 획득 • 캐시 기억장치의 해당 주소에 데이터와 태그 저장

직접 사상의 동작 • 중앙 처리장치가 00010번지 워드를 필요하는 경우

직접 사상의 동작 • 처음의 2-bits(00)는 태그를 표시하고, 다음 3-bits(010)는 캐시 기억장치의 주소를 표시. 캐시 기억장치에서 010번지 획득, 태그가 00으로 일치 • 캐시 기억장치에서 워드 획득

연관사상(Associative mapping) • 주기억장치의 블록이 캐시의 어느 라인에든 적재될 수 있어 직접사상에서 발생하는 단점을 보완 • 적중 검사가 모든 라인에 대해서 이루어져야 하므로 검사 시간이 길어진다. • 캐시 슬롯의 태그를 병렬로 검사하기 위해서는 매우 복잡하고 비용이 높은 회로가 필요하다.

집합 연관사상 (Set-associative mapping) • 직접사상과 연관사상 방식을 조합한 방식 • 하나의 주소 영역이 서로 다른 태그를 갖는 여러 개의 집합으로 이루어지는 방식 • 두 개의 집합을 갖는 집합 연관 캐시 기억장치의 구조

집합 연관사상 (Set-associative mapping) • 집합 1과 집합 2, 두 개의 집합으로 구분 • 같은 주소 번지 000 번지에 서로 다른 태그 00, 01로 구분되는 두 개의 데이터가 동시에 저장 • 동일한 주소를 가지고 다른 태그 번호를 갖는 번지에 접근하는 경우 • 직접사상의 경우 실패 • 집합 연관사상 방식의 경우 적중

두 개의 집합을 갖는 집합 연관 캐시 기억장치의 동작

교체 알고리즘(Replacement Algorithms) • 캐시 기억장치가 가득 차 있는 상태에서 캐시 기억장치의 일부를 제거하고 주기억장치로부터 새로운 데이터를 가져와야 하는 경우 캐시의 내용을 제거하는 방식 • 직접사상 방식에서는 주기억장치의 데이터가 캐시 기억장치의 같은 주소에 저장되기 때문에 교체 알고리즘을 사용할 필요가 없다. • 연관사상 및 집합 연관사상 방식의 경우 교체 알고리즘이 필요하게 된다.

쓰기 정책(Write Policy) • CPU가 프로그램을 수행하는 동안 결과를 캐시 기억장치에 쓰는 경우, 캐시 기억장치와 주기억장치에 기록하는 시점 • 즉시 쓰기(Write-though) 방식 • 모든 쓰기 동작이 캐시뿐만 아니라 주기억장치에서도 동시에 발생 • 주기억장치와 캐시 기억장치가 항상 동일한 내용을 기록 • 기억장치들 간 접근이 빈번하게 일어나고 쓰기 시간이 길어지게 된다. • 나중 쓰기(Write-back) 방식 • 새로운 데이터가 캐시에서만 갱신 • 캐시에서 데이터 내용이 변경된 적이 있다면 교체되기 전에 먼저 주기억장치에 갱신 • 주기억장치와 캐시 기억장치의 데이터가 서로 일치하지 않는 경우도 발생 • 쓰는 시간이 짧은 장점

캐시의 수(Number of Caches) • 최근에는 캐시 기억장치들이 계층적 구조로 설치 되거나 기능별로 분리된 다수의 캐시 기억장치들을 사용하는 것이 보편화 되었다. • 온-칩(On-chip) 캐시 기억장치 • 캐시 기억장치를 CPU의 내부에 포함시키는 것 • 오프-칩(Off-Chip) 캐시 기억장치 또는 외부 캐시 기억장치 • 캐시 기억장치가 CPU 외부에 위치 • 최근의 고성능 컴퓨터 들은 온-칩 캐시 기억장치와, 외부 기억장치를 동시에 포함하고 있다.

캐시의 수(Number of Caches) • 계층적 캐시(Hierarchical Cache) • 온-칩 캐시를 1차 캐시(L1)로 사용 하고 칩 외부에 더 큰 용량의 오프-칩 캐시를 2차 캐시(L2)로 설치하는 방식

계층적 캐시 기억장치 • 계층적 캐시 기억장치를 조사할 때는 먼저 L1을 검사하고 실패인 경우 L2를 검사하고 L2도 실패인 경우 주기억장치 조사 • L1 캐시기억장치는 속도는 빠르지만 용량이 작기 때문에 적중률이 L2에 비해 낮다. • 계층적 캐시 기억장치구조에서 평균기억장치 접근시간 Taverage = HL1 × TL1 + (HL2 - HL1) × TL2 + (1 - HL2) × Tmain Taverage = 평균 기억장치 접근시간 Tmain = 주기억장치 접근시간 TL1 = L1 캐시 기억장치 접근시간 TL2 = L2 캐시 기억장치 접근시간 HL1 = L1 캐시 적중률 HL2 = L2 캐시 적중률

캐시 기억장치의 통합과 분리 • 통합 캐시 • 온-칩 캐시 기억장치에서 데이터와 명령어들을 모두 저장 하는 형태 • 분리 캐시보다 적중률이 더 높다. 이유는 명령어와 데이터간의 균형을 자동적으로 유지해주기 때문이다. • 분리 캐시 • 명령어만 저장하는 명령어 캐시와 데이터만 저장하는 데이터 캐시로 분리하여 두 개의 온-칩 캐시를 사용 • 고성능 프로세서에서는 활용 경향이 뚜렷 • 장점은 명령어 인출과 실행 유니트 간 캐시의 충돌이 발생하지 않는다.

다중 프로세서를 사용하는 시스템에서의 캐시 기억장치 • 다중 프로세서 시스템 • 단일 시스템 버스에 여러 개의 CPU들이 접속 • 캐시 기억장치의 쓰기 정책인 즉시 쓰기 정책과 나중 쓰기 정책을 사용하는 경우 주기억장치와 각각의 CPU에 해당되는 캐시 기억장치들 사이에 데이터의 불일치 현상 발생 • 여러 개의 CPU와 그에 따르는 캐시들간의 데이터의 불일치 현상은 프로그램이 올바르게 동작하지 않은 원인

다중 프로세서를 사용하는 시스템에서의 캐시 기억장치

나중 쓰기(write-back) 정책에서의 데이터의 불일치 상태

캐시 기억장치의 데이터 일관성 유지 방법 • 공유 캐시 기억장치를 사용하는 방법 • 시스템에 있는 다수의 프로세서가 하나의 캐시 기억장치를 공유 • 캐시 기억장치의 데이터들이 항상 일관성 있게 유지되는 장점 • 다중 프로세서들이 동시에 캐시 기억장치에 접근하면 프로세서들간의 충돌이 발생 • 공유 변수는 캐시 기억장치에 저장하지 않는 방법 • 수정 가능한 데이터는 캐시 기억장치에 저장하지 않는 방법 • 캐시 기억장치에 저장 가능 여부를 사용자가 선택하여 선언해 주어야 하는 단점이 있다. • 버스 감시 시스템을 사용하는 방법 • 시스템 버스에 데이터의 일관성 유지를 위해 감시 기능을 가진 장비를 시스템 버스상에 추가로 설치 • 모든 데이터 들은 캐시 기억장치에 저장이 가능하며 어떤 캐시 기억장치가 데이터를 수정했다면 그 정보를 다른 캐시 기억장치와 주기억장치에 알려주게 된다. • 시스템 버스에 통신 량이 증가하는 단점이 있다.