Computers

Computers. Internal and External Memory. Characteristics of Computer Memory. Location Capacity Unit of transfer Access Method Performance Physical Type Organization. UNIVAC Console and CPU. Memory Hierarchy. COST. SPEED. REGISTERS. CACHE. MAIN MEMORY. MAGNETIC DISK | DISK CACHE.

Computers

E N D

Presentation Transcript

Computers Internal and External Memory

Characteristics of Computer Memory • Location • Capacity • Unit of transfer • Access Method • Performance • Physical Type • Organization

Memory Hierarchy COST SPEED REGISTERS CACHE MAIN MEMORY MAGNETIC DISK | DISK CACHE MAGNETIC TAPE | OPTICAL DISK

Bit Byte Kilobyte Megabyte Gigabyte Terabyte b B = 8 b KB = 1,000 B MB = 1,000,000 B GB = 1,000,000,000 B TB = 1,000,000,000,000 B Capacity Units

Memory Access Method • Sequential - tape • Direct - floppy or hard disk • Random - internal memory • Dynamic (DRAM) simple, small, must be refreshed • Static (SRAM) no refresh needed • Associative - some cache

Random Access Memory • Chips and chip technology

CONTROL read or write DATA IN / SENSE input or output SELECT select cell Memory Cells CONTROL read or write SELECT select cell 1 0/1

Write Enable Row Address Row Address Col Address ROW ADDRESS BUFFER MUX COL ADDRESS BUFFER Write to Memory Read Enable Write Enable ARRAY Col Address A0 . . . A10 ROW ADDRESS BUFFER DATA INPUT BUFFER DATA INPUT BUFFER MUX D1 . . D4 COL ADDRESS BUFFER DATA OUTPUT BUFFER REFRESH

Pin Assignments • A0 … A10: address location (multiplexed) • D1 … D4: data in or out • Vcc: power supply • Vss: ground • RAS: row address select • CAS: column address select • WE: write enable • OS: output enable

CACHE Cache Operation ALU CNTL ..... BUS MAIN MEMORY

Cache CPU Word CACHE Main Memory Block

Random Access • Direct Access Storage Device (DASD) or disk drives • Optical • Magnetic

Cylinder/Track/Block Track Block (Sector) Cylinder

DASD Structure Read-Write Heads

Data Storage • FAT (File Access Tables), Directories and Catalogs • Update and Delete • Fragmentation and reorganization • Blocks, Headers and Interblock Gaps

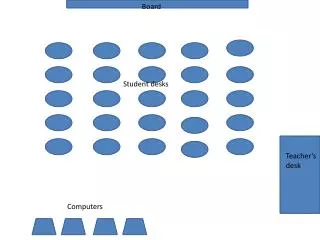

DASD Access (PC) MAIN MEMORY CPU BUFFER CACHE DASD CONTROLLER

DASD Access (Mainframe) MAIN MEMORY CPU BUFFER CHANNEL DASD CONTROLLER

Data Structure BLOCK HEADER HEADER DATA CRC • Header written when disk is formatted • Data copied into block • Cyclical Redundancy Check calculated

Controller Operation(DASD retrieval) • CPU passes parameters to registers in the controller • The controller transfers data into the card buffer • The controller checks the CRC to assure the data was copied correctly • The controller (or CPU) transfers buffered data to memory one word at a time

Millisecond Microsecond Nanosecond Picosecond ms = 1/1000 s µs = 1/1,000,000 s ns = 1/1,000,000,000 s ps = 1/1,000,000,000,000 s Time Units

Representative Times • Network speed = megabits per second • Disk transfer = megabytes per second • Disk access = milliseconds • Memory access = nanoseconds • Machine cycle = microseconds/nanoseconds

Error Correction and Checking Block Add bits to a block to use for error discovery • Detection only • Detection and retransmission • Detection and recovery Check Body Header

Error Detection Only (Asynchronous Transmission) * Parity Bit * * * * * * * 7 Data Bits 27 = 128 distinct characters

Error Detection &Correction (Hamming Code: 4 bit word) * * * 3 Error Checking Bits * * * * 4 Data Bits

Error Detection &Correction (Hamming Code: 4 bit word) DATA * * * 1 1 1 1 1 1 0 0

Error Detection PARITY (even) 100 1 1 0 1 1 1 1 1 0 0 0

Error Correction (4 bit word) PARITY (even) 100 1 1 0 1 0 0 1 1 0 0 0

Error Correction & Detection • Error detection takes fewer bits than error correction • Longer packets take a smaller percent for correction but have more types of errors • Hamming’s scheme detects all errors at a high overhead cost; others may correct only single bit or double bit errors with shorter check fields

CRC Error Checking • The transmitted messages are divided into predetermined blocks • The blocks are divided by a fixed divisor • The remainder is appended to the message