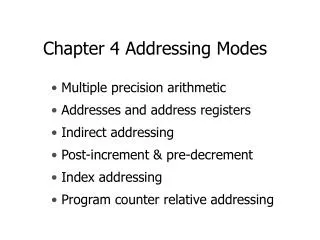

Chapter 4 Addressing Modes

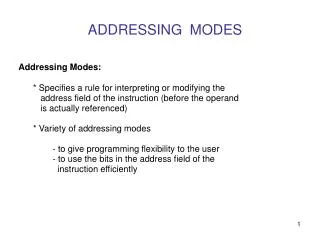

Chapter 4 Addressing Modes. Multiple precision arithmetic Addresses and address registers Indirect addressing Post-increment & pre-decrement Index addressing Program counter relative addressing. Multiple Precision Arithmetic. Memory address. PL. N.

Chapter 4 Addressing Modes

E N D

Presentation Transcript

Chapter 4 Addressing Modes Multiple precision arithmetic Addresses and address registers Indirect addressing Post-increment & pre-decrement Index addressing Program counter relative addressing

Multiple Precision Arithmetic Memory address PL N Problem: How to use an 8-bit machine to handle a 24-bit integer: R = P + Q ? PU PM PL P N + 1 PM PU : : + QU QM QL Q QL QM RU RM RL R QU RL RM RU

What is wrong? Multiple Precision Arithmetic MOVE.B PL,D0 Add lower bytes ADD.B QL,D0 MOVE.B D0,RL MOVE.B PM,D0 Add middle bytes ADD.B QM,D0 MOVE.B D0,RM MOVE.B PU,D0 Add upper bytes ADD.B QU,D0 MOVE.B D0,RU PL Problem: How to use an 8-bit machine to handle a 24-bit integer: R = P + Q ? PM PU QL QM QU RL RM RU

MOVE.B PL,D0 ADD.B QL,D0 MOVE.B D0,RL MOVE.B PM,D0 MOVE.B QM,D1 ADDX.B D0,D1 MOVE.B D1,RM MOVE.B PU,D0 MOVE.B QU,D1 ADDX.B D0,D1 MOVE.B D1,RU PL PM PU QL QM QU RL RM RU Use ADDX to add the carry out

Bytes, Words, and Longwords • MC68000 supports 8-, 16-, and 32-bit operations. • The memory is byte-addressed: when MC68000 reads a word, it gets two bytes from the consecutive locations. • All word and longword accesses must be to an even address • E.g., MOVE.L 11,D1 is invalid

1234 1234 1234 1235 1235 1235 1236 1236 1236 1237 1237 Bytes, Words, and Longwords D3 MOVE.B $1234,D3 MOVE.W $1234,D3 MOVE.L $1234,D3 Motorola 68000 is Big-Endian: The most significant byte of data is stored in the lowest address.

Byte Arithmetic Applied to Longword Register D0: 12345678 00010010001101000101011001111000 D1: 13579BDF 00010011010101111001011011011111 ADD.B D0,D1 00010011010101111001011001010111 Unaffected X N Z V C = ? Then how do we add a byte to a word?

Unsigned Integers • Larger range of integers than 2’s complement • Range of a 16-bit unsigned integer: 0 ~ 216 - 1 (65535) • Q: How are arithmetic operations performed on unsigned numbers? • Ans: No difference between signed and unsigned arithmetic interpreted by the programmer

Unsigned Integers • How do we check whether the result is out of range? • Signed: check V bit in CCR Unsigned: check C bit in CCR Unsigned Arithmetic ADD.B D1,D2 BCS ERROR : ERROR Signed Arithmetic ADD.B D1,D2 BVS ERROR : ERROR

The 68000 Address Bus • The 68000 has 32-bit address registers and program counter (PC) • Because of packaging, A24 to A31 are not used • The A00 is used to select the byte or word addressing • The 68000 has actually 24-bit addressing ! can access only 224 (16M) bytes in memory • 68020 has a full 32-bit address bus How many bytes in memory can be accessed?

Aside • In the textbook, the author said, “ For most practical purposes, 16M bytes is more than adequate.” • Quiz: Who said, “640K ought to be enough for anybody.”? Is it a) Bill Gates b) Steve Jobs c) Gordon Moore or d) Chi-Cheng Lin e) Gary Stroebel

Using Address Registers Address Registers: A0 to A7. Instructions: MOVEA, ADDA, SUBA, CMPA They do not affect the CCR.

Using Address Registers • Data registers support byte, word, and longword operations. • Address registers support word and longword operations. • 32-bit address stored in an address register is a “single entity” • Effect of a word operation to the content of an address register is a longword operation.

Using Address Registers • All MC68000’s addresses are sign-extended to 32 bits for word operations. • “ADDA.L #$FFF4,A0” will add $0000FFF4 to A0. • “ADDA.W #$FFF4,A0” will have $FFF4 sign extended to $FFFFFFF4 before addition happens. • Advantage of word operation? Consider 00000414 D1FC00000001 ADDA.L #1,A0 0000041A D0FC0001 ADDA.W #1,A0

A0 N-3 A0 A0 N N A0 N+4 Modification of the Address Register ADDA.W #-3,A0 ADDA.W #4,A0

Is “absolute addressing” a good idea? What about program “relocation” in the memory? What about multiprogramming system? Absolute Addressing MOVE.L D3,$1234 [M($1234)] [D3(0:31)] MOVE.W $1234,D3 [D3(0:15)] [M($1234)]

Register Indirect with Displacement • Extension of address register indirect • with specification of displacement or offset • Written in the form (d16,Ai) or d16(Ai), where • d16 represents a 16-bit signed displacement (Note: no ‘#’ needed for d16) • range of displacement = ? • Effective address of operand EA = d16 + [Ai] • Example: (Fig4.10 on p143, EA= 8+123416= 123C16) MOVE.W (8,A0),D0 or MOVE.W 8(A0),D0

MOVE.W (-6,A0),D0 MOVE.W -6(A0),D0 Register Indirect with Displacement D0 1232 1234 or (-6,A0) 1236 1238 123A 123C 123C A0 Our assembler only recognizes this format.

A0 2000 Error 2000 Status 2001 Input 2002 2003 Flag 2004 2005 Register Indirect with Displacement • Why is this addressing mode useful? • Support tables, arrays, structures, records, classes, etc. • Support relocation of program/data area Data area can be relocated easily • Example:

A0 2000 Error 2000 Status 2001 Input 2002 2003 Flag 2004 2005 Example: Relocatable Program Error EQU 0 offset Status EQU 1 offset Input EQU 2 offset Flag EQU 3 offset : ORG $2000 DataArea EQU * * means LC DS.B 1024 : MOVEA.L #DataArea,A0 MOVE.B Error(A0),D3 CMPI.B #12,Flag(A0) ORG $2000 Error DS.B 1 Status DS.B 1 Input DS.B 1 Flag DS.B 1 : MOVE.B Error,D3 Compared to

Example: Character Translation (Page 145 & Fig4.12) ASCII Code • How is a hex digit printed as a character? • Formula: HexChar := HexVal + $30 IF HexChar > $39 THEN HexChar := HexChar + $07 • Try verifying for ‘7’ and ‘E’

MOVE.B #8,D1 LOOP ROL.L #4,D2 MOVE.B D2,D3 ANDI.L #$0000000F,D3 MOVEA.L D3,A0 MOVE.B TRANS(A0),D0 BSR PRINT_CHAR SUB.B #1,D1 BNE LOOP Example: Character Translation Using Table Lookup (Page 145 & Fig4.12) Offset TRANS $30 0 $31 1 $32 2 : $39 9 $41 10 = A : $46 15 = F D2: 21A3485C 00100001101000110100100001011100 00011010001101001000010111000010 D3: 00011010001101001000010111000010 00000000000000000000000000000010

LEA (Load Effective Address) • Computes the effective address of an operand and loads it into an address register • Intrinsically a longword operation => .L is not required • Example LEA $0010FFFF,A5 [A5] $0010FFFF LEA (A0),A5 [A5] [A0] LEA (12,A0),A5 [A5] [A0]+12 LEA (12,A0,D4.L),A5 [A5] 12+[A0]+[D4]

Address Address 0 Data Data Data Problem: Append a new item to the linked list. Example: linked list Head Chain of items, with each item composed of head and tail The head points to the next item The tail stores a data item The last item has a null address

1000 1008 1010 1018 1018 0 1010 2000 0 1008 1125 ABCD 1125 2345 12FC 1234 12FC 2345 1234 1000 1008 1004 1000 1008 1125 1008 1004 1125 1010 100C 1010 1008 1010 2345 2345 100C 1014 1018 1010 1018 1018 12FC 1014 12FC 101C 2000 1018 0 1234 101C 1234 0 2004 ABCD Before After 1000 Before After LEA HEAD,A0 LOOP TST.L (A0) BEQ EXIT MOVEA.L (A0),A0 BRA LOOP EXIT LEA NEW,A1 MOVE.L A1,(A0) CLR.L (A1) MOVE.L data,4(A1)

MOVE.B (A0)+,D3 ;[D3(0:7)] [M([A0])] [A0] [A0]+1 MOVE.W (A0)+,D3 ;[D3(0:15)] [M([A0])] [A0] [A0]+2 MOVE.L (A0)+,D3 ;[D3] [M([A0])] [A0] [A0]+4 MOVE.B (A7)+,D4 ;[D4(0:7)] [M([A7])] [A7] [A7]+2 Address Post-incrementing Special case: A7 is stack pointer, increased by 2 with byte addressing Example MOVE.B #16,D0 LEA BUFFER,A0 LP CLR.B (A0) ADDA.L #1,A0 SUB.B #1,D0 BNE LP MOVE.B #16,D0 LEA BUFFER,A0 LP CLR.B (A0)+ SUB.B #1,D0 BNE LP

* What does this program do? (page154) TABLE_1 EQU $002000 TABEL_2 EQU $003000 N EQU $30 : LEA TABLE_1,A0 LEA TABLE_2,A1 MOVE.B #N,D0 NEXT CMPM.B (A0)+,(A1)+ BNE FAIL SUB.B #1,D0 BNE NEXT SUCCESS : : FAIL : Post-Increment Example

More Post-incrementing Example What does this program do? * Page 104 CLR.B D0 MOVEA.L #$2000,A0 NEXT ADD.B (A0),D0 ADDA.L #1,A0 CMPA.L #$2064,A0 BNE NEXT CLR.B D0 MOVEA.L #$2000,A0 NEXT ADD.B (A0)+,D0 CMPA.L #$2064,A0 BNE NEXT

* What does this program do? (Revision of ex. on page 115) ORG $400 MOVEA.L #DATA,A0 A0 points to array CLR.B D0 MAX <- 0 NEXT MOVE.B (A0)+,D1 (Modified) BEQ EXIT while not end of data CMP.B D0,D1 if (array element X BLE ENDTEST > MAX) MOVE.B D1,D0 MAX <- X ENDTEST BRA NEXT EXIT STOP #$2700 ORG $1000 DATA DC.B 12,13,5,6,4,8,4,10,0 END $400 More Post-incrementing Example

MOVE.W -(A7),D4 [A7]<-[A7]-2 [D4(0:15)]<-[M([A7])] MOVE.L -(A0),D3 [A0]<-[A0]-4 [D3]<-[M([A0])] Address Pre-decrementing • Why are post-incrementing and pre-decrementing useful? • Why is one “post” and the other “pre”? • A table can be stepped through • top-down, using post-incrementing • bottom-up, using pre-decrementing • Stack Operations (Push and Pop)

* Copy from BUFFER to BUFFER1 MOVE.B #16,D0 LEA BUFFER,A0 A0 points to top of src. LEA BUFFER1,A1 A1 points to top of dest. LP1 MOVE.B (A0)+,(A1)+ Copy SUB.B #1,D0 BNE LP1 * Copy from BUFFER1 back to BUFFER in reverse order MOVE.B #16,D0 LEA BUFFER,A0 A0 points to top of src. LP2 MOVE.B -(A1),(A0)+ Copy SUB.B #1,D0 BNE LP2 Pre-decrementing Example (Page 156)

MOVE.B #8,D0 LEA BUFFER,A0 A0 points to top LEA 16(A0),A1 A1 points to bottom LP MOVE.B (A0),D3 Swap MOVE.B -(A1),(A0)+ item from top down & MOVE.B D3,(A1) item from bottom up SUB.B #1,D0 BNE LP * Compare to the example on Page 156 Pre-decrementing Example

A1 D1 D0 A1 A1 N N-1 X N Stack 1. 2. N-1 N-1 N-1 X X N N N 2. 1. X Initially PUSH D0 MOVE.B D0,-(A1) POP D1 MOVE.B (A1)+,D1

Stack • The stack grows upward toward the low address when items are pushed to the top of the stack. • The stack pointer always points to the top item on the stack. • When an item is pushed, • the stack pointer is decreased to point to the consecutive memory above • then the new item is added onto the stack • When an item is popped, • the item on the top is copied to destination • then the stack pointer is increased to point to the consecutive memory below

Index Addressing • Displacement addressing: Fixed offset • Index addressing: Variable offset • Operand: (d8,An,Xm.W) or (d8,An,Xm.L) d8(An,Xm.W) or d8(An,Xm.L) d8: 8-bit 2’s complement signed integer An: address register Xm: used for indexing, either Ax or Dx Our assembler only recognizes this format.

EA = d8 + [An] + [Xm] Examples: Index Addressing MOVE.L (A1,D0.L),D3 [D3] [M([A1]+[D0])] MOVE.L 3(A1,D0.L),D3 [D3] [M(3+[A1]+[D0])] MOVE.L 3(A1,D0.W),D3 [D3] [M(3+[A1]+[D0(0:15)])] Example: Fig 4.22, p159 Index addressing is useful to implement and manipulate arrays.

Arrays • One-dimensional array is stored in consecutive memory locations. • Issues: • How can we “declare” a 1-D array? • Where can we locate an element of a 1-D array in memory?

Arrays • How can we “declare” a 1-D array? • Examples: • Array1 DS.B 9 array of 9 bytes • Array2 DS.W 5 array of 5 words • Array3 DC.B 2,4,5,6,1,3 * array of 6 bytes with initial values

4 1000 2 1001 7 1002 1 1003 3 1004 7 1005 4 1006 3 1007 1 1008 Arrays • Where can we locate an element of a 1-D array in memory? • The location of the ith element is Base + (i-1) x element_size • Example: • Array1 DC.B 4,2,7,1,3,7,4,3,1 Note: Element_size is measured in byte • The 5th element is in location 1000 + (5-1) x 1 = 1004 • Is this element Array1[5] or Array1[4]?

Two-dimensional Matrix • A two-dimensional matrix (or array) is mapped onto a one-dimensional memory array. • An m by n array, Amxn means an array of m rows, n columns. • Issues: • How can we “declare” a 2-D array? • Where can we locate an element of a 2-D array in memory? n m

Two-dimensional Matrix • How can we “declare” a 2-D array? • Examples • 5 by 3 array of bytes Array1 DS.B 15 • 4 by 6 array of words Array2 DS.W 24 • 3 by 4 array of 3-byte integers Array3 DS.B 36 • DC.x can be used to initialize arrays

4 2 7 1 3 7 4 3 1 Two-dimensional Matrix Where can we locate an element of a 2-D array in memory? • In row order, the location of in Amxn is Base + ((i-1) x n + (j-1)) x element_size 1000 1001 1002 1003 1004 1005 1006 1007 What about Column order? 1008 Where is a3,2?

Two-dimensional Matrix • Using index addressing: • In row order, EA of in Amxn can be obtained by d8(Ax,Dy), where Ax = Base of array Dy = (i-1) x n x element_size d8 = (j-1) x element_size • EA of = d8 + [Ax] + [Dy] = Base + ((i-1) x n + (j-1)) x element_size

Two-dimensional Matrix • Of course, if the index begin with 0, • In row order, EA of in Amxn can be obtained by d8(Ax,Dy), where Ax = Base of array Dy = i x n x element_size d8 = j x element_size • EA of = d8 + [Ax] + [Dy] = Base + (i x n + j) x element_size

Two-dimensional Matrix • The calculation in the previous two slides works only when j is a constant. If j is a variable, we cannot use d8. • In row order, EA of in Amxn can be obtained by (Ax,Dy), where • Ax = Base of array • If the index begins with 1 Dy = ((i-1) x n + (j-1)) x element_size If the index begins with 0 Dy = (i x n + j) x element_size

A: 1 22 3 10 12 0 A0 (A0,D2.W) [D2]=2 Matrix Calculation: C = A + B (p163) * A, B, C are m by n matrices * c i,j = a i, j + b i, j LEA A,A0 LEA B,A1 LEA C,A2 MOVE.W #m,D0 D0: row counter CLR.W D2 L2 MOVE.W #n,D1 D1: col. counter L1 MOVE.B (A0,D2.W),D6 ADD.B (A1,D2.W),D6 MOVE.B D6,(A2,D2.W) ADD.W #1,D2 SUB.W #1,D1 BNE L1 SUB.W #1,D0 BNE L2

Matrix Calculation: C = A + B (p164) LEA A,A0 LEA B,A1 LEA C,A2 MOVE.W #m*n,D0 D0: element counter L1 MOVE.B (A0)+,D6 ADD.B (A1)+,D6 MOVE.B D6,(A2)+ SUB.W #1,D0 BNE L1

Program Counter Relative Addressing Special case of register indirect Two modes: displacement: EA = [pc] + d16 index: EA = [PC] + [Xn] + d8

MOVE.B TABLE(PC),D2 … TABLE DC.B Value1 DC.B Value2 Program Counter Relative Addressing When the code is assembled, the assembler uses the offset TABLE (or relative address of TABLE) to calculate (memory_loc_of_TABLE - [PC]) When the instruction is executed, the offset is added to current PC to give the address of TABLE

1 00001000 ORG $1000 2 00001000 143900002000 MOVE.B TABLE,D2 3 00001006 4E722700 STOP #$2700 4 5 00002000 ORG $2000 6 00002000 0F TABLE: DC.B $0F 7 00001000 END $1000 1 00001000 ORG $1000 2 00001000 143A0FFE MOVE.B TABLE(PC),D2 3 00001004 4E722700 STOP #$2700 4 5 00002000 ORG $2000 6 00002000 0F TABLE: DC.B $0F 7 00001000 END $1000 Program Counter Relative Addressing 2000 - 1002