Modern processor design

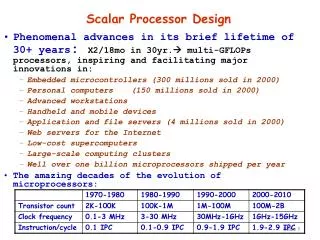

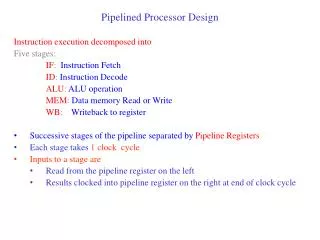

Modern processor design. Engineering design. The dynamic-static interface (DSI). Conceptuall illustration of possible placement of DSI in ISA design. Performance simulation metods. Trace-driven simulation. Execution-driven simulation. Scalar pipeline machine.

Modern processor design

E N D

Presentation Transcript

Conceptuall illustration of possible placement of DSI in ISA design

Performance simulation metods Trace-driven simulation Execution-driven simulation

Superpipelined MIPS R4000 8-stage pipeline

Pipeline example 4-stage 11-stage

Impact on ALU, Load, and Branch penalties with increasing pipeline depth

Parallel pipeline - examples 5-stage Pentium parallel pipeline s=2 5-stage i486

Interpipeline-stage buffers single-entry buffer multi-entry buffer multi-entry buffer with reordering

Dynamic pipeline with reservation stations and reorder buffer