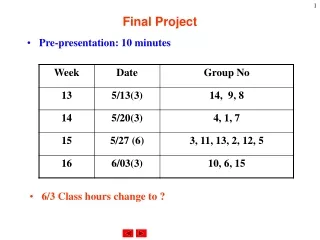

Final Project

Final Project. System Overview. Description of Inputs. reset: When LOW, a power on reset is performed. mode: When LOW, NORMal mode selected When HIGH, CONFIG mode selected. clk: Master clock input str: When in NORM mode, this is string to be decypted.

Final Project

E N D

Presentation Transcript

Description of Inputs reset: When LOW, a power on reset is performed. mode: When LOW, NORMal mode selected When HIGH, CONFIG mode selected. clk: Master clock input str: When in NORM mode, this is string to be decypted. Asynchronous input stream. Self-clocking!!! When in CONFIG mode, this will be configuration data. Synchronous input stream!

CONFIG Mode n 4-bit binary value denoting the length of d and N parameters d The decryption key. It is 2**n bits long. N This is the modulus. It is also 2**n bits long. Total length of configuration data is 2**(n+1) + 4 bits long!!! Configuration data is synchronized to clk. Legal values of n are between 3 and 10.

Self-clocking (asynchronous) of data in NORM mode Bit period will be at least 50 clock cycles but not more than 1000! If we stay LOW for a complete bit period or HIGH for a complete bit Period (previous bit period) then a break as occurred and you may abort!

Description of Outputs msg The decypted message. It is exactly 2**n bits long and sync’ed to clock. Changes on this line are in response to rising edge of clk. frame This output should go HIGH to indicate that there is valid data on the msg pin. Transitions in frame signal should be sync’ed to the rising edge of clk. Should remain high for 2**n clock cycles.

RSA Primer S = s**e modulo N encrypt s = S**d modulo N decrypt If d is 13, n is 8, N is 62 and S= 27 then s = (27 ** 13) modulo 62 = 29 Note: 2**8 is 256 so N, s, and S are all 256 bits long.

Verilog Lab #3 Design a serial adder circuit using Verilog. The circuit should add two 8-bit numbers, A and B. The result should be stored back into the A register. Use the diagram below to guide you. Hint: Write one module to describe the datapath and a second module to describe the control. Annotate your simvision trace output to demonstrate that the adder works correctly. Demonstrate by adding $45 to $10 in your testbench.

Controller and Datapath Modules module serial_adder_datapath(sum, sout, sinA, sinB, ctl, reset, clk) ; output [7:0] sum ; output sout ; input sinA, sinB ; input [ ] ctl ; input reset, clk ; endmodule module serial_adder_control(ctl, busy, start, reset, inv_clk) ; output [ ] ctl ; output busy ; input reset, start, inv_clk ; endmodule

Adder/Subtractor Assignment // 4-bit full-adder (behavioral) module fa(sum, co, a, b, ci) ; input [3:0] a, b ; input ci ; output [3:0] sum ; output co ; assign {co, sum} = a + (ci ? ~b : b) + ci ; endmodule

Serial Multiplier (Verilog) // multiplier module multiplier(S, clk, clr, Bin, Qin, C, A, Q, P) ; input S, clk, clr ; input [4:0] Bin, Qin ; output C ; output [4:0] A, Q ; output [2:0] P ; // system registers reg C ; reg [4:0] A, Q, B ; reg [2:0] P ; reg [1:0] pstate, nstate ; parameter T0 = 2'b00, T1= 2'b01, T2 = 2'b10, T3 = 2'b11 ; // combinational circuit wire Z ; assign Z = ~|P ; // state register process for controller always @(negedge clk or negedge clr) begin if (~clr) pstate <= T0 ; else pstate <= nstate ; end

// state transition process for controller always @(S or Z or pstate) begin case (pstate) T0: if (S) nstate = T1; else nstate = T0 ; T1: nstate = T2 ; T2: nstate = T3 ; T3: if (Z) nstate = T0; else nstate = T2 ; endcase end // register transfer operations always @(posedge clk) begin case (pstate) T0: B <= Bin ; T1: begin A <= 0 ; C <= 1 ; P <= 5 ; Q <= Qin ; end T2: begin P <= P - 1 ; if (Q[0]) {C,A} <= A + B ; end T3: begin C <= 0 ; A <= {C, A[4:1]} ; Q <= {A[0], Q{4:1]} ; end endcase end endmodule Serial Multiplier (Continued)

Serial Multiplier (Testbench) // multiplier testbench module multiplier_tb; reg S, clk, clr ; reg [4:0] Bin, Qin ; wire C ; wire [4:0] A, Q ; wire [2:0] P ; // instantiate multiplier multiplier uut(S, clk, clr, Bin, Qin, C, A, Q, P); // generate test vectors initial begin #0 begin S = 0; clk = 0; clr = 0 ; end #5 begin S = 1; clr = 1; Bin = 5'b10111 ; Qin = 5'b10011 ; #15 begin S = 0 ; end end

Serial Multiplier (Testbench, continued) // create dumpfile and generate clock initial begin $dumpfile("./multiplier.dmp") ; $dumpflush ; $dumpvars(2, multiplier_tb) ; repeat (26) #5 clk = ~clk ; end endmodule