Technologie

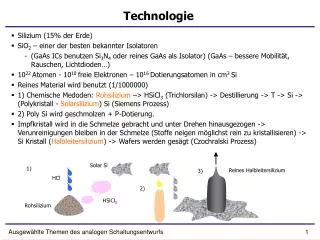

Technologie. Silizium (15% der Erde) SiO 2 – einer der besten bekannte r Isolatoren (GaAs ICs benutz en Si 3 N 4 oder reines GaAs als Isolator ) (GaAs – bessere Mobilität, Rauschen, Lichtdioden…) 10 22 Atomen - 10 10 freie Elektronen – 10 16 Dotierungsatomen in cm 3 Si

Technologie

E N D

Presentation Transcript

Technologie • Silizium (15% der Erde) • SiO2 – einer der besten bekannter Isolatoren • (GaAs ICs benutzen Si3N4 oder reines GaAs als Isolator) (GaAs – bessere Mobilität, Rauschen, Lichtdioden…) • 1022Atomen - 1010freie Elektronen – 1016 Dotierungsatomen in cm3Si • Reines Material wird benutzt (1/1000000) • 1) Chemische Medoden: Rohsilizium –> HSiCl3 (Trichlorsilan) -> Destillierung -> T -> Si -> (Polykristall - Solarsilizium) Si (Siemens Prozess) • 2) Poly Si wird geschmolzen + P-Dotierung. • Impfkristall wird in die Schmelze gebracht und unter Drehen hinausgezogen -> Verunreinigungen bleiben in der Schmelze (Stoffe neigen möglichst rein zu kristallisieren) -> Si Kristall (Halbleitersilizium) -> Wafers werden gesägt (Czochralski Prozess) Solar Si 1) Reines Halbleitersilizium 3) HCl 2) HSiCl3 Rohsilizium Ausgewählte Themen des analogen Schaltungsentwurfs

Technologie Front-End Prozesse – Erzeugung von Transistoren Deponierung von Dotierungssubstanzen, Oxidation, Isolierung von Transistoren Back-End Prozesse – Erzeugung von Metalllagen (Al, Cu), Isolatorlagen (SiO2, Glas), „Via“ Löcher (Wolfram). Photolithographie Schritte: Polymer Photolack wird aufgebracht Stepper wird benutzt: „Reticle“-Dia mit 5X Verkleinerung mittels UV Licht (200 nm) wird projiziert. Photolack wird belichtet, belichtete Stellen härten NaOH wird benutzt, Photolack durch Ätzung entfernt Elektronenstrahllithographie Ausgewählte Themen des analogen Schaltungsentwurfs

Technologie – Implantation von Diffusionswannen • Standard N-Well Prozess mit epi-Lage • Wafer (Monokristall) • Schritt 1 • Epi Lage – ein epitaktisch gewachsene Si Schicht (Monokristall) • Schritt 2 • Schwachdotierte N- und P-Wannen für P und N-Kanal Transistoren werden erzeugt • Maske ist SiO2 • Oxidation • Nitrid wird aufgebracht • Photolack • Ätzung. • Ionen (P) werden mit 80KV beschleunigt, Ionenimplantation, Dotierung… Ausgewählte Themen des analogen Schaltungsentwurfs

UV Licht SiO2 Epi Lage Photolack Si2N3 Epi Lage SiO2 Ionenimplantation Wafer Epi Lage Wafer Si2N3 Wafer SiO2 Epi Lage Ätzen Wafer Implantation von Diffusionswannen Ausgewählte Themen des analogen Schaltungsentwurfs

Feldoxid Dickes Oxid (Feldoxid) – Isolierung zwischen Transistoren Maske: SiO2 + Silizium-Nitrid „LOCOS“: Lokale „feuchte“ Oxidation: Si + 2H2O - > SiO2 + 2H2 (Oberfläche nicht eben) „STI“: Plasma Ätzung – Trench – CVD (Chemical Vapour Deposition) Oxid (benutzt Gas Si(OC2H5)4 ) – Polieren (CMP – Chemical Mechanical Polishing) – ebene Oberfläche – erlaubt mehr Metalllagen. Ausgewählte Themen des analogen Schaltungsentwurfs

Si2N3 SiO2 Epi Lage Wafer Lack Si2N3 H2O SiO2 SiO2 SiO2 Oxidation Feldoxid Anisotropische Ätzung u. Polieren Ätzen Ausgewählte Themen des analogen Schaltungsentwurfs

Gate Oxid • Transistoren (aktive Bereiche) und ohmsche Kontakte sind jetzt isoliert. • Der kritischste Schritt – Erzeugung vom Gate – Oxid • Trockene thermische Oxidierung (in Sauerstoff Atmosphäre) 100 min @ 800°C. (Si + O2 -> SiO2) – 7nm Oxid Ausgewählte Themen des analogen Schaltungsentwurfs

800° C 02 Oxidation Epi Lage Gate Oxid Ausgewählte Themen des analogen Schaltungsentwurfs

Transistor • Ganzflächige Abscheidung von Polysilizium – ( CVD ) (Silan – SiH4). • Photolack + Polysilizium wird abgeätzt – Gate Elektroden. • Maske deckt die aktive Bereiche ab. • Rundumisolierung von Gate Elektroden „spacer“ definiert schwach dotierte Source und Drain • As (Arsen) und P (Phosphor) Ionen – n+ Drain, Source, ohmsche Kontakte – Polysilizium Gates dienen als Masken – Prozess ist selbstjustierend (self-aligment) • B (Bor) Ionen – p+ Drain, Source, ohmsche Kontakte • Thermische Ausheilung – Diffusion von Ionen . • Ti wird angebracht – TiSi2 bildet sich am Silizium – SiO2 Oberfläche reagiert nicht – Ti wird abgeätzt – (self aligned silicide) Ausgewählte Themen des analogen Schaltungsentwurfs

thermische Ausheilung SiH4 Oxidation Chemische Abscheidung Poly Si P+ P+ Transistor Ionenimplantation Photolack Poly-Silizium Ausgewählte Themen des analogen Schaltungsentwurfs

Silizierung (TiSi2) Metallisierung (selbstjustierendes Silizid) Aufbringen gasförmigen Titans Ätzung Anisotropische Ätzung Poly Si Ausgewählte Themen des analogen Schaltungsentwurfs

Metallisierung • SiO2 und Phosphorglas werden angebracht • 1) „Via“ Öffnungen werden gemacht • 2) und mit Titan und Wolfram aufgefüllt • 3) Polieren • 4) Aufbringen von Dielektrikum • 5) Sputtern von Al oder Cu • 6) Metall wird strukturiert • 7) Polieren • … • Passivierung • Die letzte Maske – Öffnungen in Passivierung Ausgewählte Themen des analogen Schaltungsentwurfs

Strukturierung Aufbringen vom Dielektrikum Sputtern von Al oder Cu Aufbringen von Wolfram Metallisierung Aufbringen von SiO2 und Bor-Phosphor-Silikat-Glas Poly Si Ausgewählte Themen des analogen Schaltungsentwurfs