Understanding the Execution Flow of MIPS Assembly Instructions

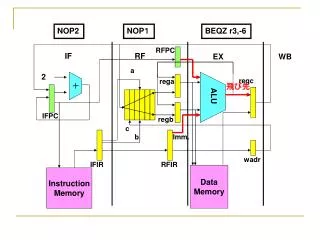

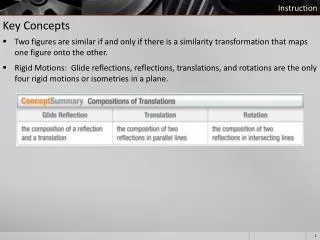

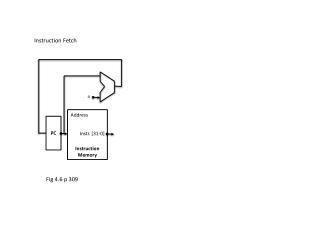

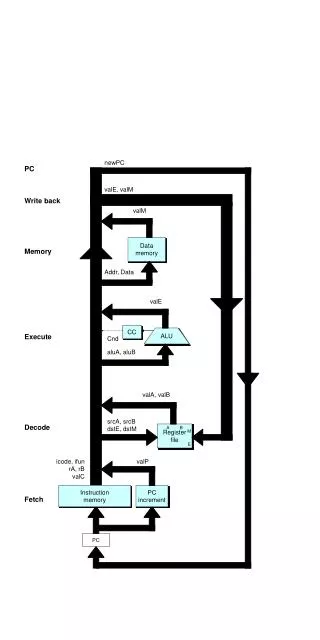

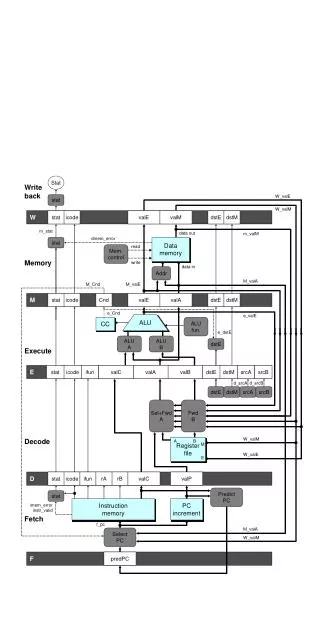

This document explores the MIPS assembly instruction flow, specifically focusing on instructions like NOP and BEQZ. It breaks down the pipeline stages: Instruction Fetch (IF), Register Fetch (RF), Execution (EX), Write Back (WB), and how branches are managed. The use of registers, immediate values, and memory operations are also discussed, providing insights into how the MIPS architecture processes instructions and transitions between various stages. The analysis is crucial for those studying computer architecture and assembly language programming.

Understanding the Execution Flow of MIPS Assembly Instructions

E N D

Presentation Transcript

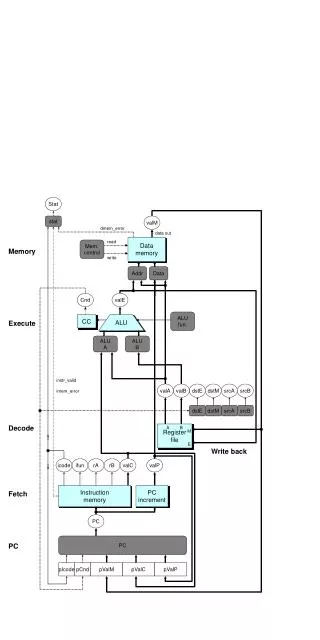

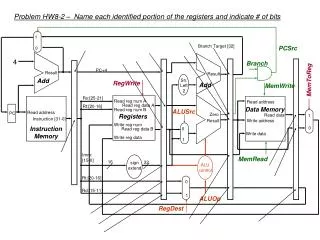

NOP2 NOP1 BEQZ r3,-6 RFPC IF RF EX WB a 2 regc rega + 飛び先 ALU IFPC regb c b Imm. wadr IFIR RFIR Data Memory Instruction Memory

NOP3 NOP2 NOP1 BEQZ r3,-6 RFPC IF RF EX WB a 2 regc rega + ALU IFPC regb c b Imm. wadr IFIR RFIR Data Memory Instruction Memory

BEQZ r3,-6 NOP1 IF RF EX WB + 2 regc rega a + ALU IFPC regb c b Imm. wadr IFIR RFIR Data Memory Instruction Memory

Next Inst. NOP1 BEQZ r3,-6 IF RF EX WB + 2 regc rega a + ALU IFPC regb c b Imm. wadr IFIR RFIR Data Memory Instruction Memory