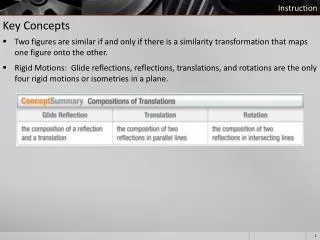

Instruction Memory

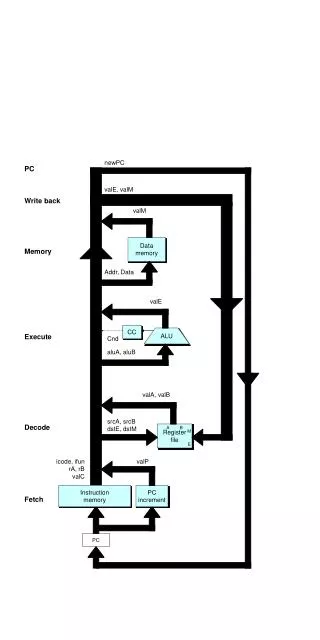

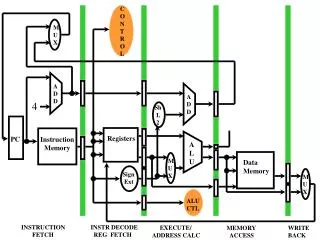

Instruction Fetch. Instruction Memory. Address. 4. Instr. [31-0]. PC. Fig 4.6 p 309. Write. Data Memory. Address. Write data. Data. Read. Registers and ALU. Instr [25-21 ] ( rs ). Instr [20-16 ] ( rt ). Registers. Read r eg 1. Read d ata 1. Instr [15-11 ] ( rd ). Read

Instruction Memory

E N D

Presentation Transcript

Instruction Fetch Instruction Memory Address 4 Instr. [31-0] PC Fig 4.6 p 309

Write Data Memory Address Write data Data Read

Registers and ALU Instr [25-21] (rs) Instr[20-16] (rt) Registers Read reg 1 Read data 1 Instr [15-11] (rd) Read reg 2 Read data 2 zero Write reg ALU Ctrl result 16 Sign Ext 32 Instr[15-0] ALU Write data Instr [5-0] 0 0 From figures 4.7, 4.8 pp 310-311. MUX MUX 1 1

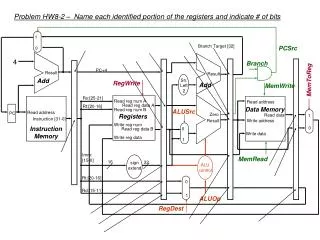

RegDst Control Branch MemRead MemToReg Instr[31-26] ALUOp MemWrite ALUSrc RegWrite

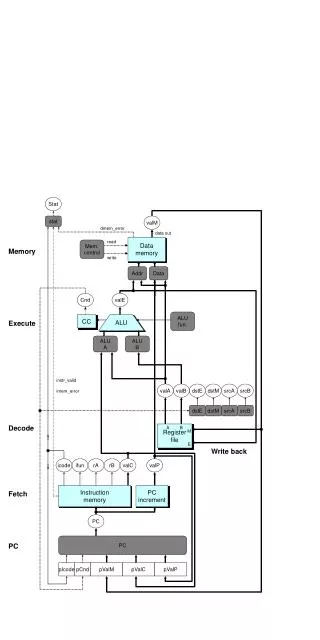

Add Add 4 Shift Left 2 RegDst Control Branch MemRead MemToReg Instr[31-26] ALUOp MemWrite ALUSrc Registers Read reg 1 Read data 1 Data Memory Instruction Memory RegWrite Address Address Instr [25-21] Data Read reg 2 Instr. [31-0] Read data 2 PC Instr[20-16] zero Write reg result ALU Write data Write data Instr [15-11] 1 0 0 0 ALU Ctrl MUX MUX MUX 16 Sign Ext MUX 32 Instr [15-0] 1 0 1 1 Instr [5-0] Figure 4.17 p322

Add Add 4 Shift Left 2 Control Instr[31-26] Registers Read reg 1 Read data 1 Data Memory Instruction Memory Address Address Instr [25-21] Data Read reg 2 Instr. [31-0] Read data 2 PC Instr[20-16] zero Write reg result ALU Write data Write data Instr [15-11] 0 0 0 0 ALU Ctrl MUX MUX MUX 16 Sign Ext MUX 32 Instr [15-0] 1 1 1 1 Instr [5-0]

Add Add Shift Left 2 Control Registers Read reg 1 Read data 1 Data Memory Instruction Memory Address Address Data Read reg 2 Instr. [31-0] Read data 2 PC zero Write reg result Write data ALU Write data 0 0 0 0 ALU Ctrl MUX MUX MUX MUX Sign Ext 1 1 1 1