Partial Evaluation Based Redundancy for SEU Mitigation in Combinational Circuits

190 likes | 327 Views

Partial Evaluation Based Redundancy for SEU Mitigation in Combinational Circuits. MAPLD 2005 BOF-L Mitigation Methods for Reprogrammable Logic in the Space Radiation Environment Sujana Kakarla & Srinivas Katkoori {kakarla, katkoori}@cse.usf.edu Computer Science & Engineering

Partial Evaluation Based Redundancy for SEU Mitigation in Combinational Circuits

E N D

Presentation Transcript

Partial Evaluation Based Redundancy for SEU Mitigation in Combinational Circuits MAPLD 2005 BOF-L Mitigation Methods for Reprogrammable Logic in the Space Radiation Environment Sujana Kakarla & Srinivas Katkoori {kakarla, katkoori}@cse.usf.edu Computer Science & Engineering University of South Florida

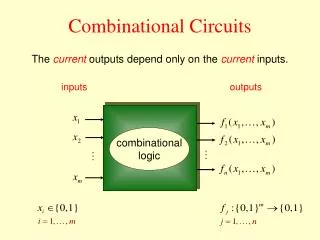

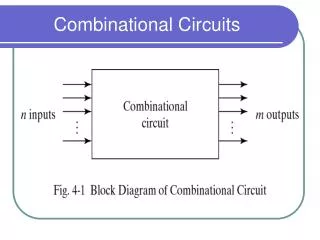

Partial Evaluation Based Triple Modular Redundancy • Observation If some input values are known in advance • The entire circuit need not be triplicated • Gates with constant output can be eliminated • Functionally equivalent reduced circuit is obtained • Triplicate the reduced circuit

Partial Evaluation • Widely used in the software applications • Not popular in hardware because of its static nature • Optimization by exploiting prior knowledge • Functional level Partial Evaluation • Propagate known values throughout the function • Obtain new specialized function • Done at run time • Techniques: Symbolic computation, Loop unrolling, Memoization, etc., • Advantages: • Speed up • Efficient and modular solution

Temporal TMR Majority voter circuit for T-TMR Original circuit Final output delay unit delay unit Majority voter circuit for PE Reduced circuit select line Reduced circuit Logic for select line of multiplexer Spatial TMR

Temporal TMR is used in cases when the actual inputs to the circuit are not in accordance with the rounded values B = 0.46 C = 0.84 Need for Temporal TMR A = 0.124 0 A ‘rounded’ to 0 0 B = 0.46 0.3864 C = 0.84 A = 0 B = 1 C = 0 Out = 0 A = 0 B = 1 C = 0 Out = 0 A = 1 B = 1 C = 0 Out = 1 A = 1 B = 1 C = 0 Out =0 Incorrect Output!

Temporal TMR Circuit Voter circuit Delay Unit Delay Unit

Partial Evaluation TMR Flow Step 1 Rounding probabilities Step 5 Determine output from Temporal TMR circuit Step 2 Propagate probabilities Resolve logic on signals Step 6 Selection of output from the two sets of values Step 3 Obtain functionally equivalent reduced circuit Step 7 Validation Step 4 Determine output from Partially evaluated circuit

Step 1: Rounding the probabilities • If the input probabilities are such that 0.0 ≤ p ≤ 0.2 => logic value = ‘0’ 0.9 ≤ p ≤ 1.0 => logic value = ‘1’ • The rounded probability values are then propagated over the circuit

Step 3: Redundant gate elimination • All redundant gates are eliminated • “not” gate cannot be eliminated • Gates in the last level cannot be eliminated

Step 4: TMR Insertion • The reduced circuit is duplicated • A majority voter is used at each output Original Circuit Majority Voter Circuit Reduced Circuit Correct output Reduced Circuit

Step 5: Temporal TMR • For temporal TMR, pass each of the output through a series of two delay units • We now have the output determined at three instances of time • A majority voter is used to determine the correct output Majority Voter Circuit Correct output Original Circuit Delay unit Delay unit

Step 6: Output Selection • Two sets of output values, one set from partial evaluation based TMR the other from Temporal TMR • Multiplexer selects the correct output among the two sets • Suppose probability of input A, p is such that 0.9 ≤ p ≤ 1.0 probability of input B, q is such that 0.1 ≤ q ≤ 0.2 then the select line for the multiplexer is Ā + B

Step 7: Validation Original circuit • Faults representing SEUs are introduced into the circuit using a SEU simulator • Faulted circuit is functionally verified using NC Cadence Launch • Outputs of the original circuit without faults and outputs of the faulted circuit are compared to check if any fault has propagated to the output Implementation of partial evaluation Reduced circuit SEU Simulator Simulate original circuit Simulate faulted circuit Comparison Results

Delay overhead Temporal TMR PE based TMR Spatial TMR Area overhead Advantages and Disadvantages of Partial Evaluation based TMR • Advantages • Less area overhead • Power savings • High tolerance to SEUs • Disadvantages • In the worst case, area overhead is greater than the full TMR • Delay overhead when Temporal TMR is used

PTMR - Conclusions • Greater savings in area are obtained for circuits with more number of gates and with less number of primary outputs • The area overhead for the technique is proportional to the number of primary outputs • Area overhead of PTMR circuit is less than TMR but has greater delay overhead • Delay overhead of PTMR is less than Temporal TMR