Unit 9 Multiplexers, Decoder, and Programmable logic Devices ( 멀티플렉서 , 디코더 , 프로그래머블 논리소자 )

Unit 9 Multiplexers, Decoder, and Programmable logic Devices ( 멀티플렉서 , 디코더 , 프로그래머블 논리소자 ). 강의 개요. 멀티플렉서 , 디코더 , 프로그래머블 논리소자 멀티플렉서 3-State Buffer 디코더와 인코더 읽기 전용 메모리 Programmable Logic Device PLA(Programmable Logic Array) PAL(Programmable Array Logic)

Unit 9 Multiplexers, Decoder, and Programmable logic Devices ( 멀티플렉서 , 디코더 , 프로그래머블 논리소자 )

E N D

Presentation Transcript

Unit 9 Multiplexers, Decoder, and Programmable logic Devices (멀티플렉서, 디코더, 프로그래머블 논리소자)

강의 개요 • 멀티플렉서, 디코더, 프로그래머블 논리소자 • 멀티플렉서 • 3-State Buffer • 디코더와 인코더 • 읽기 전용 메모리 • Programmable Logic Device • PLA(Programmable Logic Array) • PAL(Programmable Array Logic) • CPLD(Complex Programmable Logic Devices) • FPGA(Field Programmable Gate Array)

9.2 Multiplexer • 멀티플렉서(Multiplexer, 데이터 선택기, MUX ) • 데이터 입력과 제어 입력으로 구성된 소자. • 제어 입력은 데이타 입력 중에서 하나를 선택하여 출력단과 연결하는 역할을 한다. • 2-to-1 멀티플렉서 및 등가 스위치

9.2 Multiplexer • 여러 가지 멀티플레서들

9.2 Multiplexer • 멀티플렉서는 디지털 시스템에서 처리되거나 저장되는 데이터를 선택하는데 자주 사용된다. • 4개의 2-to-1 멀티플렉서를 이용한 데이터 워드 선택 구현 • 제어입력 A에 따라 다른 워드 선택 • A = 0 : x0, x1, x2, x3 • A = 1 : z0, z1, z2, z3

9.2 Multiplexer • Bus • 여러 개의 논리 신호가 공통된 기능을 수행하기 위해 그룹화 된 것 • 여러 개의 선을 다 그리는 대신 하나의 굵은 선과 사선을 이용하여 표현 • 4 bit 입력과 출력을 가지는 2-to-1 멀티플렉서

9.2 Multiplexer • 다양한 멀티플렉서들 • 선택된 입력 값을 반전시켜 출력하는 멀티플렉서 • Active low 상태 출력을 가짐 • 반전이 없는 경우는 Active high 상태 출력을 가진다고 함 • Enable 단자를 가지는 멀티플렉서 • 멀티플렉서의 입력에 Enable 단자를 추가 • E (Enable) = 0 인 경우 입력에 무관하게 출력은 0 • E = 1 인 경우 멀티플렉서로 동작 • Enable 단자 역시 Active high/low 존재 • Enable 단자의 버블 유무로 구별 가능

9.3 Three-State Buffers • 버퍼(Buffer) • 디지털 시스템의 성능을 저하를 피하기 위해 게이트의 출력을 제한된 수의 다른 소자의 입력에만 연결하는 경우가 있다. • 버퍼는 게이트 출력의 구동 능력을 향상시키기 위해 사용된다. • 예시 : 비반전 버퍼를 추가하여 하나의 게이트 출력과 다수의 게이트 입력을 연결

9.3 Three-State Buffers • 2개 이상의 게이트 또는 다른 소자들의 출력들이 서로 직접 연결 된다면 정상상태에서 논리회로는 올바르게 동작하지 않는다. • 하나의 게이트 출력이 0이고 또 다른 게이트의 출력이 1일 때, 두 출력이 서로 연결된 경우 결과 출력 전압은 0 이나 1로 뚜렷이 구별되지 않는 중간 값을 갖게 된다. • 어떤 경우에는 게이트가 파손되기도 한다.

9.3 Three-State Buffers • 3-state buffer • 2개 이상의 게이트나 다른 논리소자들의 출력을 서로 연결하는 데 사용 • 3-state buffer와 그 논리적 등가모델 • B는동작 허용 입력 • B=1 일 때 C=A • B=0 일 때 C=Z (High Impedance/개방회로) • Three-state or Tri-state Buffer라 불림

9.3 Three-State Buffers • 4가지 3-state buffer와 그 논리표 • Enable 단자 B와 출력 C에 버블의 유무에 따라 4가지 경우 존재

9.3 Three-State Buffers • 3-state buffer를 이용한 데이터 선택 • 3-state buffer로 구성된 버스를 3-state 버스라 함 • 4개의 발생원으로부터 operand를 입력 받는 4비트 덧셈기 • B=0이면 D=A 이므로 A 입력 선택 • B=1이면 D=C 이므로 C 입력 선택 • 2-to-1 멀티플렉서와 동등

9.3 Three-State Buffers • 양방향 입출력을 가진 집적회로 • 하나의 핀을 때에 따라 입/출력으로 사용할 수 있는 회로 • 버퍼가 동작 가능 상태 : 출력 • 버퍼가 동작 불가능 상태 : 입력

9.4 Decoders and Encoders • 디코더(Decoder) • n 개의입력변수를 가진 함수의 모든 최소항(2^n)을 생성한다. • 입력변수에 따라 출력 선 중 단 하나만이 1이 된다. • 3-to-9 라인 디코더와 진리표

9.4 Decoders and Encoders • 반전 출력을 가지는 디코더 • 4-to-10 디코더 • 나머지 ABCD 입력은 모두 1 • 2진수 입력에 해당하는 10진수 출력

9.4 Decoders and Encoders • 일반적인 n-to-2n 라인디코더는 n개의 입력에 대해 아래와 같은 출력을 가진다. • m은 n개의 입력변수의 최소항 • M은 n개의 입력변수의 최대항 • n입력 디코더를이용하여 n-변수 함수를 최소항 출력들을 선택한 뒤 OR 함으로써 구현 가능 • 디코더 출력을 반전하면 NAND 게이트로 구현 가능

9.4 Decoders and Encoders • 디코더 출력 반전 - NAND 게이트를 이용하여 함수 생성

9.4 Decoders and Encoders • 인코더 • 디코더의 Inverse Function • 2n-to-n 입출력 • 8-to-3 인코더 • 입력의 하나 이상이 ‘1’인 경우 우선순위에 의해 결정됨

9.5 Read-Only Memories • ROM(Read-Only Memory) • 2진데이터배열을 저장하기 위해 상호 연결된 반도체 소자의 배열로 구성 • 읽을 수는 있지만 변경할 수는 없음 • 예시: 3개의 입력선과 4개의 출력선을 가지는 ROM • ROM에저장되는 각각의 출력 패턴을 워드(word)라 부른다.

9.5 Read-Only Memories • n개의 입력을 가지는 경우 2n가지의 다른 조합을 가짐 • 입력 선은 2n 개의 워드 중 하나의 주소의 역할 • m개의 출력을 가지면 워드의 길이는 m비트 • n개의 변수를 가지는 m개의 함수 구현 가능

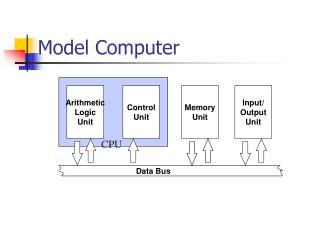

9.5 Read-Only Memories • 기본적인 ROM 구조 • n개의 패턴이 디코더에 인가 • 디코더 출력 중 하나가 ‘1’이 됨 • 이 출력 선 하나가 메모리 배열의 하나인 워드를 선택하여 출력

9.5 Read-Only Memories • 8워드 4비트 ROM 내부구조 예시 • 스위칭 소자에 의해 출력선 F에 연결된 최소항들은 서로 OR되어 출력을 생성 함

9.5 Read-Only Memories • ROM을 이용한 다중 출력 조합회로 구현 • 예제: 16진수-ASCII Code 변환기 • 4비트 2진수를 16비트로 변환 • 7비트 ASCII Code 출력 • 진리표의 A4A3A2A1A0이 ROM에 저장

9.5 Read-Only Memories • 스위칭 소자는 x 표시로 나타낼 수 있음 • 위 예제의 내부 도표

9.5 Read-Only Memories • 대표적인 ROM의 종류 • Mask-Programmable ROM • 생산공정시 데이터 배열이 영구적으로 저장 • PROM(Programmable ROM) • 아무 내용이 들어있지 않은 빈 상태로 제조하여 공급되고 사용자가 PROM 라이터를 이용하여 내용을 써넣을 수 있음 • EEPROM(Electrically Erasable Programmable ROM) • 디지털 시스템 개발 과정 중 이용 • 전하 저장 장치를 사용하여 재 프로그램 가능 • cf) 플래시는 프로그래밍 및 소거 기능을 내장하고 있음

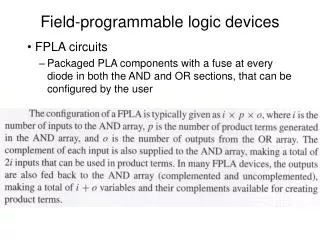

9.6 Programmable Logic Devices • Programmable Logic Device • 다양한 논리 함수를 제공하도록 프로그램이 가능한 디지털 집적회로 • Programmable Logic Array • ROM과 동일한 기본 기능을 수행 • n개의 입력과 m개의 출력을 가질 경우 n개의 변수를 가진 m개의 함수 구현 가능 • PLA는 논리곱의 합 표현을 구현함 • (ROM은 진리표를 그대로 구현) • ROM의 디코더 • ->AND Array로 대체되어 곱 항 실현 • OR 배열은 선택된 곱 항을 OR 하여 출력 실현

9.6 Programmable Logic Devices • ROM과 PLA의 비교 ROM PLA

9.6 Programmable Logic Devices • 앞 예제와 등가인 PLA

9.6 Programmable Logic Devices • PLA를 이용한 최소 다중 출력 함수 구현 • PLA Table을 생성한 후 PLA 구조 구현 • PLA table의 각 행은 최소항을 나타냄

9.6 Programmable Logic Devices • Programmable Array Logic(PAL) • AND 배열은 프로그램이 가능하지만 OR 배열은 고정되어 있는 특별한 형태의 PLA • PAL은 하나의 입력이 많은 수의 AND 게이트를 구동하기 때문에 버퍼를 사용함 • 프로그램을 하지 않은 상태의 PAL의 일부분 • 논리적으로 동등한 입력 버퍼

9.6 Programmable Logic Devices • 예제1: I1I’2+I’1I2함수를 PAL로 구현 • PAL의 일부분 사용

9.6 Programmable Logic Devices • 예제2: 전가산기(Full-Adder) 를 PAL로 설계하기 • 전가산기의 논리식

9.7 Complex Programmable Logic Devices • CPLD(Complex Programmable Logic Devices) • 하나의칩 안에 여러 개의 PAL 또는 PLA를 집적하여 연결한 논리소자 • 기억소자가 같이 집적된다면 하나의 디지털 시스템을 CPLD안에 구현 가능함 • CPLD 내부의 상호 연결은 컴퓨터 소프트웨어로 설계 가능 • Xilinx CPLD 구조 및 회로

9.8 Field Programmable Gate Array • FPGA(Field Programmable Gate Array) • 프로그램이가능한 연결선들과 함께 동일한 기능을 가지는 논리 셀들의 배열을 가지는 집적회로 • 논리 셀들 간의 연결선을 이용하여 함수를 프로그램 할 수 있음 • CLB(Configurable Logic Block)들의배열로 구성되어 있음 • CLB는 I/O 블록으로 둘러쌓여 있음 FPGA의 Layout

9.8 Field Programmable Gate Array • CLB • 내부 interconnection을 위한 다양한MUX 가짐 • 함수 발생기는 LUT(Look-up Table)에의해 구현 • 4변수 함수 발생기 • ROM • 생성하고자 하는 함수의 진리표 저장 • LUT • 최소항을 몇 개 가지건 하나의 함수발생기가 필요함 CLB LUT 구현

9.8 Field Programmable Gate Array • 스위칭 함수의 분할 • 4개 이상의 변수를 가지는 스위칭 함수를 4-변수 함수 발생기를 이용하여 구현하기 • 스위칭 함수를 4-변수를 가지는 서브함수로 분할 • 샤논의 정리를 이용 - 변수 xi에 대하여 n 변수 함수를 전개 • f0 : 원래 함수에서 xi 를 0으로 하여 얻은 (n-1)개의 변수를 갖는 함수 • f1 : 원래 함수에서 xi 를 1로 하여 얻은 (n-1)개의 변수를 갖는 함수

9.8 Field Programmable Gate Array • 예제1: 5-변수 함수를 4-변수 함수 발생기로 구현 • 5개 변수를 갖는 어떠한 함수도 2개의 4-변수 함수 발생기와 하나의 2-to-1 MUX를 가지고 구현할 수 있음을 나타냄 • 예제2: 6-변수 함수를 4-변수 함수 발생기로 구현 • 샤논의 전개이론을 두 번 적용 • G00, G01, G10, G11 은모두 4-변수 함수

9.8 Field Programmable Gate Array • 4-입력 함수발생기를 예제 1번과 2번 함수의 구현 • n (n>4) 변수 함수는 2n-4개의 4-변수 함수발생기와 2n-4-to-1 MUX를 이용하여 구현할 수 있음