Chapter 7 전계 효과 트랜지스터

470 likes | 2.45k Views

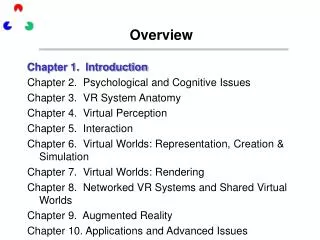

Chapter 7 전계 효과 트랜지스터. 목 표. 접합 전계 효과 트랜지스터 (JFET) 의 동작과 특성 고찰. JFET 파라미터의 정의와 적용. JFET 바이어스 회로 해석. 금속 산화물 반도체 전계 효과 트랜지스터 (MOSFET ; M etal O xide S emiconductor F ield E ffect T ransistors ) 의 동작과 특성 고찰. MOS FET 파라미터의 정의와 적용. MOSFET 바이어스 해석. 개 요.

Chapter 7 전계 효과 트랜지스터

E N D

Presentation Transcript

목 표 • 접합 전계 효과 트랜지스터(JFET)의 동작과 특성 고찰 • JFET 파라미터의 정의와 적용 • JFET 바이어스 회로 해석 • 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET ; Metal Oxide Semiconductor Field Effect Transistors)의 동작과 특성 고찰 • MOSFET 파라미터의 정의와 적용 • MOSFET 바이어스 해석

개 요 • 전계 효과 트랜지스터는 게이트(gate)에 공급되는 • (게이트와 소스 사이의) 전압에 의해 전류가 조절되는 • 전압제어 소자(하나의 반송자를 이용하는 단극소자) • 바이폴라 접합 트랜지스터(BJT)는 전자전류와 • 정공전류를 이용한 전류제어 소자 • FET는 BJT에 비해 매우 높은 입력저항을 가지는 장점 • FET는 BJT와 동일하게 이용

7-1. JFET • JFET는 BJT처럼 전류 흐름을 제어 • - JFET는 게이트와 소스 사이에 공급하는 전압에 의해 전류의 흐름을 제어 • BJT에서는 베이스-이미터 접합의 제어 전류에 의해 전류의 흐름을 제어 • JFET는 BJT와 같이 증폭기로 이용 VGG전압이VDD와 RD회로에 흐르는 전류 흐름 제어

JFET의 기본 구조와 기호 • JFET의단자 – 소스(source), 게이트(gate), 드레인(drain) • JFET의종류 – p-채널,n-채널 JFET의 기본 구조 JFET의 기호

JFET의 기본 동작 • 전류는 게이트-소스 접합에 역방향바이어스를 걸어 pn 접합면에 공핍층을 형성하게 하여 채널의 폭을 조절함으로써 전류의 흐름을 제어(게이트는 양단이 동일하게 연결) • VGG (역방향바이어스)의 변화에 따라 공핍층이 확장 및 축소되면서 채널폭이 변화하게 되어RD를 통해 흐르는 전류 흐름 ID를 제어 • 드레인-게이트간의 역방향 전압이 • 게이트-소스간의 역방향 전압보다 • 크기 때문에 공핍영역이 드레인쪽으로 • 더 확산 바이어스된 n-채널 JFET

7-2. JFET 특성과 파라미터 • 게이트-소스전압이 0일 때(VGS = 0V), 드레인-소스간이 단락 • VDD를 0V에서 점점 증가시키면 ID가 비례적으로 증가 • (VDD가 증가되는 것처럼 VDS가 증가). • 점 A와 B 구간을 저항영역(ohmic region) 드레인 특성 곡선

핀치-오프 전압 • 점 B에서 직선은 증가를 멈추고 ID 값이 일정 • - VGS = 0V일 때 핀치-오프전압(pinch-off voltage) • VDS가 계속 증가하더라도 드레인 전류가 일정 • (이때의 드레인 전류를 최대 드레인 전류 ; IDSS) • VDS를 증가시켜 점 C에 도달하면 항복현상(breakdown)이 발생 • 항복현상은 소자에 치명적이므로 JFET는 이 점 이하의 일정한 전류 영역에서 동작되어야 함. 핀치-오프 전압

VGS에 의한 ID제어 • 게이트와 소스에 바이어스 전압 VGG를 인가하고, VGG를 조절하여 VGS가 음(-)의 값으로 증가하면 ID가 감소 VGS를 변화 시켰을 때의 드레인 전류의 변화 곡선

차단 전압 • VGS를증가시키면 ID가 거의 0으로 감소되는데 이를 차단현상(cutoff)이라 하고, 이때의 VGS를 차단전압(VP ;cutoff voltage) • 공핍 영역은 VGS가 음(-)의 값으로 증가할수록 더욱 확장하여 핀치오프 현상이 발생하게 되어 ID가 거의 0으로 감소 • ID는 IDSS의 최대값에서 거의 0인 최소값까지 변화 가능 • (VGS의 변화에 의해) 차단상태의 JFET

JFET 전달 특성 • 전달특성 곡선은 차단 전압(V GS(off) )과 핀치-오프 전압(VP) 사이에서 제어되는 VGS와 ID 의 관계를 도시 • JFET의특성곡선은 거의 포물선 형태이고, 이를 근사적으로 표현하면ID= IDSS(1 - VGS/VGS(off))2 JFET의 전달특성 곡선

JFET의 파라미터 • 순방향 전달 컨덕턴스 gm은 드레인-소스 전압이 일정할 때 게이트-소스 전압의 변화분(△VGS)에 대한 드레인 전류의 변화분(△ID)의 비 gm= △ID/△VGS • 게이트-소스 접합에 역방향 바이어스를 가하면 JFET의 입력저항은 매우 크게 증가(BJT에 비해 좋은 장점) • 역방향 바이어스된 pn 접합은 커패시터로 동작하며, 그 용량은 역방향 전압의 크기에 의존 RIN= |VGS/IGSS| • 드레인-소스 저항은 VDS와 ID의 변화율(핀치-오프 위의 영역에서는 VDS의 변화에도 ID가 거의 일정하므로 VDS의 큰 변화는ID의 작은 변화를 야기 r’ds= △VDS/△ID

7-3. JFET 바이어스 • BJT와 마찬가지로 바이어스의 목적은 직류 게이트-소스 전압을 선택하여 바람직한 드레인 전류값과 적절한 Q 점을 선택하는 것 • JFET 바이어스 – 자기바이어스(self-bias), 전압분배 바이어스(voltage-divider bias) • Q 점은 전달특성 곡선의 중간부분에서 선택되는데 이는 최대 드레인 전류의 IDSS중간값

자기 바이어스 • JFET의 가장 일반적인 방법 • 게이트-소스전압 VGS는 n-채널은 (-), p-채널은 (+) • 게이트에 공급하는 전압이 없기 때문에 VG=0V이고, • 저항 RG는 바이어스에 영향을 미치지 않고 증폭기 • 응용시 접지로부터 교류신호를 분리할 때 사용 • 게이트-소스 전압은 (ID= IS, VG=0이므로 VS=IDRS) • VGS = VG-VS=0-IDRS=-IDRS • (n channel) VGS = -IDRS • (p channel) VGS = +IDRS • 접지를 기준으로 한 드레인 전압은 • VD=VDD-IDRD • VS=IDRS로 부터 드레인-소스 전압을 구하면 • VDS=VD-VS=VDD-ID(RD+RS) 자기 바이어스된 JFET

자기 바이어스된 JFET의 Q 점 결정 • JFET의 바이어스 점은 VGS값에 대한 ID또는 특정 ID값에 대한 VGS의 값으로 결정 • Q점결정을 위한 RS는ID 와VGS로 결정 • RS= | VGS/ID | • VGS값에 대해 ID는 두 가지 방법으로 결정 • - JFET의 전달특성 곡선 • - 규격표의 IDSS와VGS(off)를 사용한 다음의 • 식으로부터 • ID= IDSS(1 - VGS/VGS(off))2

중간점 바이어스 • ID=IDSS/2 되는 전달특성 곡선의 중간점에 JFET를바이어스 시키는 것이 중요 • 신호 조건하에서 중간점 바이어스는 IDSS와 0사이에서 드레인 전류의 스윙이 최대 • RS와 RD 는 근사화된 중간점 바이어스를 위해 결정 • RS= |VGS/ID | • RD = (VDD/2)/ID • 아래의 조건과 같을 때 ID가 IDSS의 거의 반 • VGS VGS(off)/3.4

JFET의 전달특성곡선과 임의의 파라미터를 사용하여 자기 바이어스된 회로의 Q점을 결정하는 것이 가능 • 먼저 규격표의IDSS와 다음의 공식을 이용하여 VGS를 결정 • VGS = -IDRS • 부하선과 전달특성곡선의 교차점이 회로의 Q점 • 부하선은 VGS(off)(ID= 0A)인 점과 VP(ID = IDSS)인 점을 연결한 것 JFET의 부하점 결정

전압분배 바이어스 • R1과R2에는게이트-소스 접합간의 역방향 바이어스를 위해 VDD가 적절하게 분배 • 동작은 자기 바이어스와 동일 • ID, VGS를 결정하기 위해서는 VS = IDRS(ID=IS) VG = (R2/(R1 + R2))VDD VGS = VG– VS VS = VG – VGS ID=VS/RS ID=(VG-VGS)/RS 전압분배 바이어스

자기 바이어스와 마찬가지로 전달특성 곡선으로부터 Q점 결정 가능 첫번째 점은ID = 0 과VGS (ID=0 일 때 VGS = VG). VGS = VG = (R2/R1 + R2)VDD 두번쨰 점은ID, VGS= 0. ID = VG/RS 전압분배 바이어스의 직류부하선

Q 점의 안정도 • 같은 형태의 소자라도 • JFET의 전달특성은 • 매우 상이 • 이는 Q점 결정에 좋지 • 않은 영향을 미침 • 전압분배 바이어스는 • 자기 바이어스보다 덜 영향 Q 점의 안정도

7-4. MOSFET • 금속 산화물 반도체 전계 효과 트랜지스터( Metal Oxide Semiconductor Field Eeffect Ttransistor ; MOSFET)는 FET의 두번째 형태 • pn 접합 구조가 아니라는 면에서 JFET와 상이 • MOSFET의 게이트는 산화실리콘(Sio2) 층에 의해 채널과 격리 • MOSFET는 공핍형(depletion MOSFET ; D-MOSFET)과 증가형 (enhancement MOSFET ; E-MOSFET) • E-MOSFET는 채널의 형성되어있지 않음. D-MOSFET의 기호 D-MOSFET의 구조

공핍형 MOSFET • D-MOSFET는 공핍형과 증가형 모드로 분류 • 공핍형 모드는 부(-)의 게이트-소스 전압을 인가하여 동작하고, 정(+)의 전압을 인가하면 증가형 모드로 동작 • 공핍형 모드 – 게이트에 (-) 전압을 인가하면 채널내의 전도전자를 밀어내고, 그 자리에 양이온이 발생하여 채널내의 전도전자가 부족하게 되고 드레인 전류가 감소하게 되므로 (-) 전압을 VGS(off)로 하면 채널이 완전 공핍되어 드레인 전류가 0 D-MOSFET의 동작(공핍형) • 증가형 모드 – 게이트에 (+) 전압을 인가하면 채널내로 전도전자를 끌어 들여 채널내의 전도전자가 증가하게 되어 채널의 전도도가 증가함으로써 드레인 전류가 증가 D-MOSFET의 동작(증가형)

증가형 MOSFET • E-MOSFET는 증가형 모드로만 동작하고, 구조적 채널 미 존재 • 게이트에 (-) 전압을 인가하면 SiO2층의 접촉면에 얇은 음전하층의 채널이 형성 • 게이트-소스간의 전압이 증가할 수록 기판의 전도전자를 더 끌어들여 채널의 전도도 증가 • 기호에서 점선은 물리적인 채널이 존재하지 않음을 의미 E-MOSFET의 구조 E-MOSFET의 기호

기타 MOSFET 측면 이중 확산 MOSFET(LDMOSFET) 와 V형 MOSFET(VMOSFET), TMOSFET는고전력에 이용하기 위해 고안된 구조 이중 게이트 MOSFET는 두개의 게이트를 가지며, FET의 결점인 높은 입력 커패시턴스로 인한 고주파에서의 사용 제한을 완화 LDMOSFET VMOSFET 이중 게이트 MOSFET TMOSFET

7-5. MOSFET 특성과 파라미터 D-MOSFET의 전달특성 D-MOSFET(증가형 모드)는 JFET의 특성과 파라미터가 적용 가능 ID는 증가형과 공핍형 모드에서 똑같이 적용가능하고, JFET와 동일 ID = IDSS(1 - VGS/VGS(off) )2 D-MOSFET의 전달특성 곡선

E-MOSFET의 전달특성 • E-MOSFET는 채널 증가만 이용 • VGS가 임계값 VGS(th)에 도달할 때까지 드레인 전류 가 존재하지 않음. • E-MOSFET의 전달특성 곡선은 JFET와 D_MOSFET의 식과는 상이 • 상수K는 MOSFET의 종류에 따라 다르며, 규격표에서 VGS가 주어졌을 때 ID(on)인 ID값으로 아래의 공식으로 유도 • K = ID(on) /(VGS - VGS(th))2 ,ID= K(VGS - VGS(th))2 E-MOSFET의 전달특성 곡선

7-6. MOSFET 바이어스 D-MOSFET의 바이어스 • MOSFET의 바이어스 : 제로 바이어스, 전압분배 바이어스, 드레인 귀환 바이어스 • D-MOSFET의 바이어스인 제로 바이어스는 VGS=0으로 하고, 게이트에 교류신호를 인가하여 바이어스 점에서 입력된 전압에 따라 게이트-소스 전압이 변동(swing)하도록 동작 D-MOSFET의 제로 바이어스

E-MOSFET의 바이어스 • E-MOSFET는 제로 바이어스를 사용 못함. • 전압분배 바이어스는 VGS를 임계값VGS(th)보다 크게 하기 위함. • ID는 다음의 공식에 의해 유도(VGS는일반적인 전압분배 방식으로) • K = ID(on)/(VGS - VGS(th))2 • ID = K(VGS -VGS(th))2 • VDS = VDD-IDRD E-MOSFET의 바이어스 • 드레인 귀환 바이어스는 게이트 전류가 무시되므로 RG에서의 전압강하가 없어 VGS = VDS • ID 는 다음에 의해 유도 가능 • ID = VDD - VDS/RD