VLSI Design Project Progress and Layout Development Summary

370 likes | 463 Views

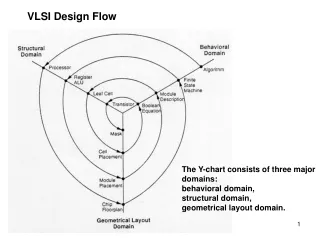

Explore the development of a ring oscillator concept using VHDL and ModelSim. Learn layout techniques and verification in IC Station. Simulate the gate characteristics with Eldo for detailed analysis.

VLSI Design Project Progress and Layout Development Summary

E N D

Presentation Transcript

VLSI Design Third Year Standard Project - SB1 Second Mini Lecture Web page: https://camtools.cam.ac.uk David M Holburn David ChuahJiming Jiang 12th May - 6th June 2009

Summary of progress so far • Developed ring oscillator (RO) concept • Confirmed using VHDL & ModelSim • Explored effect of varying NOR delays (ModelSim) • Built symbol & schematic • Incorporated RO in Frequency Synthesiser design • Used Eldo to predict timing characteristics of RO using AMS NOR2 design • Investigated characteristics of real RO design using oscilloscope/counter

Labs 5 & 6 Lab Guide 5 • Gain familiarity with layout and IC Station layout editor • Adaptmask layouts for the 2-input NOR gate nor2x • Identify/correct design rule violations in nor2 layout Lab Guide 6 • Verification - check for proper correspondence between your nor2x layout & the nor2x transistor schematic • Check transistor dimensions W & L • Investigate effect of parasitic elements C and R in layout • Simulate the gate’s characteristics with parasitics using Eldo

Layout and stick diagrams p and n-type MOSFETchannels MOSFET channels and interconnect Interconnect,channels and gate electrodes

Layout and stick diagrams (2) Input Contact cuts(one of four) Output

Form Factor Identical logic functions Channels aligned horizontallyShort, wide form factor Channels aligned verticallyTall, thin form factor

VDD D D S S VSS Stick diagrams: NAND Input A Output Input B

Output in polySicrosses under VDD VDD VSS Stick diagrams: NOR Input B NB: contact cutlinks m1 and poly Output wired in metal 1 Input A

Design rules Mask : Poly1 4A Minimum poly1 width 0.35m Current density must not exceed 500A/m 4C Minimum Poly1 spacing or notch width 0.45 m 4D Minimum Poly1 to Diffusion spacing 0.20 m 4B Minimum Gate length (0.35 m) 4E Minimum Poly1 extension on field oxide 0.40 m 4F Minimum source and drain width 0.50 m

Lab Guide 5 - layout of nor2x • IC Station operations • familiarise with basic techniques • study & understand layout • detect & correct rule violations • add gate electrodes • connect output • consider how to optimise layout • size • speed • convenience of input/output • compatible with other cells • plot completed layout

Final week – Complete System Lab Guide 7 • Use Design Architect-IC to create top-level schematic • Incorporates all design blocks • Programmable divider and its sub-blocks • Ring Oscillator • Single NOR gate • Input/Output and Power pads • Simulate entire system using Eldo • May take several minutes to run!

Final week - Semi Custom Design Lab Guide 8 • Use IC Station, ICassemble & ICBlocks • Create complete IC layout for synthesiser module • Automatic and interactive floor-planning • Automatic cell placement • Automatic routing of interconnect • Flattened and Hierarchical designs • Generate colour check plot of result • Your design is complete!

Hierarchical layout design • Hierarchy - a methodology for creating larger design from smaller design objects • At lowest level objects are polygons, shapes and paths (leaf cells), e.g. nor2, nand2 • Inserted in a multi-tiered, hierarchical design • Designer controls visibility of detail • Allows construction of libraries of commonly used parts e.g. divider (based on count4) • Permits re-use of designs in other projects

Hierarchical Objects comparator divider ring_oscillator control single_nor

Place & Route standard cells All nets shown yellow are routed right away - unrouted nets in green