Electronics Beyond Nano-scale CMOS

Electronics Beyond Nano-scale CMOS. Shekhar Borkar Intel Corp. July 27, 2006. Outline. Evolution of Electronics to CMOS The three tenets Technology outlook Challenges Potential solutions Summary. Performance Energy Price/Performance. Evolution of Electronics. Mechanical.

Electronics Beyond Nano-scale CMOS

E N D

Presentation Transcript

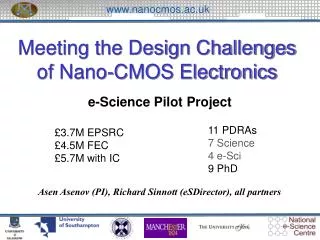

Electronics Beyond Nano-scale CMOS Shekhar Borkar Intel Corp. July 27, 2006

Outline • Evolution of Electronics to CMOS • The three tenets • Technology outlook • Challenges • Potential solutions • Summary

Performance Energy Price/Performance Evolution of Electronics Mechanical Electro-Mechanical Electronic-VT • All cross-road technologies show • Gain • Signal/Noise • Scalability Bipolar NMOS CMOS……. ?

Energy Signal/ Noise Gain Input Input Output Output (2) (1) Scalability, in some shape or form (3) The Three Tenets

1928, Otis Elevator Electro-Mechanical scaling—Relays

Vacuum Tubes 1930’s 1920’s 1950’s & 60’s

Semiconductors The first transistor Pentium® 4 The first integrated circuit 4004

Manufacturing Development Research Carbon Nanotube FET 5 nm 50 nm 30 nm Nanowire 35 nm 20 nm 10 nm S D S Metal Gate III-V High-k Tri-Gate G Si Substrate CMOS Research Continues… Technology Generation 90 nm 65 nm 45 nm 32 nm 2004 2006 2008 2010 2012+ SiGe S/D Strained Silicon SiGe S/D Strained Silicon

What’s in sight after CMOS? • Which technology shows gain? • Satisfactory signal to noise ratio? • At room temperature? • Scalability in some shape or form? • Performance, Energy, Cost • Research must continue to find one • Then it will take 10-15 years to mature • Until then… CMOS will continue…

Source: Mark Bohr, Intel Lithography Wavelength 365nm 248nm 193nm 180nm 130nm 90nm Gap 65nm 45nm Generation 32nm 13nm EUV Random Dopant Fluctuations Sub-wavelength Lithography Heat Flux (W/cm2)—Vcc variation Temp Variation & Hot spots …But With Challenges!

Vdd Vdd Ip Op Op Vss Vss Yesterday’s Freelance Layout No layout restrictions

Vdd Vdd Ip Op Op Vss Vss Transistor Orientation Restrictions Transistor orientation restricted to improve manufacturing control

Transistor Width Quantization Vdd Vdd Op Ip Op Vss Vss

Wider Extreme device variations Soft Error FIT/Chip (Logic & Mem) Burn-in may phase out…? Time dependent device degradation Reliability

Implications to Reliability • Extreme variations (Static & Dynamic) will result in unreliable components • Impossible to design reliable system as we know today • Transient errors (Soft Errors) • Gradual errors (Variations) • Time dependent (Degradation) Reliable systems with unreliable components —Resilient mArchitectures

Implications to Design & Test • Design with regular fabric • One-time-factory testing will be out • Burn-in to catch chip infant-mortality will not be practical • Test HW will be part of the design • Dynamically self-test, detect errors, reconfigure, & adapt

100 Billion Transistors 100 BT integration capacity Billions unusable (variations) Some will fail over time Intermittent failures In a Nut-shell… Yet, deliver high performance in the power & cost envelope

Recipe for Resiliency • Circuit • Firmware • Platform • Software • Application • Detect • Isolate • Confine • Reconfigure • Recover & adapt

C C C C C C C C C C C C C C C C Resiliency with Reconfiguration • Dynamic on-chip testing • Performance profiling • Spare hardware • Binning strategy • Dynamic, fine grain, performance and power management • Coarse-grain redundancy checking • Dynamic error detection & reconfiguration • Decommission aging HW, swap with spare • Dynamically… • Self test & detect • Isolate errors • Confine • Reconfigure, and • Adapt

Litho Cost FAB Cost G. Moore ISSCC 03 www.icknowledge.com $ per Transistor $ per MIPS Why Bother?

Summary • Three tenets: Gain, Signal/Noise, Scalability • Nothing on the horizon satisfies them • Research must continue to find one • But until then, CMOS rules • Several challenges lay ahead, but when have they not?