The Central Trigger Processor Technical Design Report

The Central Trigger Processor Technical Design Report. Presented by: O. Villalobos Baillie Univ. of Birmingham. Outline of Talk. NA57 – a prototype for ALICE Introduction to ALICE system Design considerations The Central Trigger Processor Layout Dynamic Partitioning

The Central Trigger Processor Technical Design Report

E N D

Presentation Transcript

The Central Trigger ProcessorTechnical Design Report Presented by: O. Villalobos Baillie Univ. of Birmingham O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

Outline of Talk • NA57 – a prototype for ALICE • Introduction to ALICE system • Design considerations • The Central Trigger Processor • Layout • Dynamic Partitioning • Past-future Protection • Outputs and data • Scalers • Region-of-Interest Option • The Local Trigger Unit • Context • Emulation mode • Connections • Current status • Software • Organization • Software choices • Control software • Project Organization • Summary O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

NA57 Trigger – A Prototype for ALICE • VME trigger system designed for NA57, allowing 6 trigger classes from 20 inputs. • System foresaw dynamic partitioning, trigger modification if buffering nearly full, and many other ALICE features. Not all were used in NA57 context. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

NA57 Electronics • NA57 electronics system was built in 6U VME using ALTERA FPGAs. Example above shows one board (TMX). • System shown to be stable and reliable. Control software built into the DATE package used by NA57. Good experience for ALICE. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

Design Considerations • Trigger should cope with a wide variety of different running modes, having very different rates. • Trigger should be able to allow for past-future protection. • Trigger should be able to allow for dynamic partitioning of detectors. • Trigger should provide agreed data to each sub-detector partition for each L1/L2a trigger. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

Running Conditions O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

CTP Basic Parameters • 50 Inputs • 24 L0 • 20 L1 • 6 L2 • 6 Trigger clusters (groups of detectors which read out together) • 50 trigger classes (L0, L1,L2 trigger conditions, trigger cluster, options) • 100 ns decision time • 2μs “dead time” between each L0 trigger. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

Trigger Latencies • CTP decision time 100 ns • L0 - to strobe track/hold detectors • L1 - to initiate transfer to FE buffers • L2 - to permit traffic on DDL to LDC O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

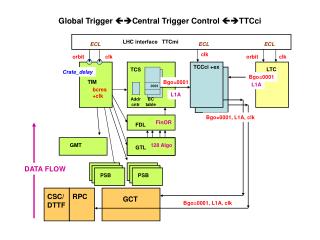

CTP Layout CTP expected to be made up of six board types in a standard 6U VME crate; Each TTC partition contains LTU and TTC interface for one detector. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

Dynamic Partitioning • Each TTC partition is addressed separately. It is therefore possible to trigger any detector independently of the others. For practical reasons, this is done for clusters of detectors. • Purpose of clusters is to take advantage of the fact that some detectors are able to cycle faster than others, and that it is possible to do useful physics without reading out the full detector. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

Past-Future Protection I • In Pb-Pb running, past-future protection should distinguish peripheral from semi-central events. An event of interest can have additional pile-up peripheral events, but not semi-central events. One pile-up window for all detectors O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

Past-Future Protection II • In pp mode, the centrality of the events is not important. However, the number of pile-up events in different windows, (e.g. ITS and TPC sensitive periods) is important. Different configuration of p/f circuit allows this type of protection to be set. Only one interaction type considered O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

CTPOutputs • Trigger has 3 levels. Trigger signals are: • Calibration pre-pulse (pulse) • L0 (pulse) • L1 (message) • L2a (message) • L2r (word) O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

CTP Data I L1 Trigger message L2 Trigger message O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

CTP Data II • CTP data record for an event contains L1 and L2 data. • In addition, interaction record notes, for each orbit, which BCs gave interactions, (whether triggered or not) and whether they were peripheral or semi-central. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

Scalers σ2 = (N5 /N4)(N3 /N2) σ0 • Scalers are kept for all inputs • For each trigger class, the triggers passing L0, L1, L2 stages (before and after applying Busy/P-F restrictions) are kept • This allows relative cross-sections to be evaluated. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

Region-of-Interest Option • The CTP foresees the future development of a Region-of-Interest Processor to specify which azimuthal sectors of the detector should be read out. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

The LTU • The Local Trigger Unit (LTU) is an interface unit between the CTP and the TTC system. • It can also be used to emulate the CTP when the LTU is used in stand-alone mode. This is particularly useful during the development of the system. • This unit needs to be the first to be produced in the trigger system. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

LTU Context • Signals and data are transferred from the CTP to the LTU using a short number of parallel transmissions • The LTU then sends these signals to the TTC system, where they are transmitted to TTCrx receivers on the FE electronics for the detector. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

LTU Emulation Mode • LTU receives signals either from CTP or from an emulator. Downstream of selector logic is the same. Creates ALICE-like environment for development work. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

LTU Connections • LTU connections fall into three types • Custom flat cable connection to CTP • LEMO type connectors (various standards) to TTC components. • LVDS connectors for fast signals directly connected to LTU. • Note oscilloscope probes used to monitor signals selected via software. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

LTU Status • PCB layout and overseeing of work done by industry all performed by RAL. • Some problems starting up – led to six month delay. • Layout completed in December. First version now produced. • First board being populated this week. It will arrive in Birmingham for testing starting next week. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

Software Development • Software development has been addressed for the Central Trigger System with two timescales in mind: • Fixing the software framework for the operation of the CTP, and its links with the ECS, DCS, and DAQ systems. (Link to HLT simpler and more limited.) • Preparing software for immediate use in testing and commissioning the LTU, which will be used by a wider group of people than the CTP software. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

Organization of Software O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

Software Choices • Trigger control and communications • SMI and DIM • GUI • Tcl/tk and/or python/tk • Monitoring • ROOT with AFFAIR package • Documentation • LaTeX/Word with eps figures • Database • No choice made yet. Can start with simple files and upgrade later O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

LTU Control Software • Our first target –needed in a few days time to start LTU testing. • Program tested using Concurrent Technologies VP-110 SBC running Linux. SBC can also simulate LTU response until board arrives. • Main feature of GUI – “VME crate” menu, from which other menus can be extracted. Model is easily expanded to other board types. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

Project Organization • Two Institutes take part in CTP project: • School of Physics and Astronomy, The University of Birmingham, Birmingham UK • D. Evans, P. Jovanović, A. Jusko, R. Lietava, O. Villalobos Baillie. • Institute of Experimental Physics, Slovak Academy of Sciences, Košice, Slovakia • L. Šándor, S. Fedor, I. Králik, J. Urbán. • Project leader: O. Villalobos Baillie. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

Principal Milestones • June 2004 - LTU delivered to collaboration. • July 2005 - CTP construction completed. • January 2006 – Trigger system at CERN for installation and commissioning. (Details of commissioning still being finalized.) O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004

Summary • Trigger project studied over a long period (NA57 prototype developed in 1997, ALICE conditions finalized in 2001). Design requirements well understood. • LTU about to start testing. First part of trigger system to be used, (in emulation mode). • Trigger software developing in parallel; avoid delays in using trigger components when they become available. O. Villalobos Baillie – Central Trigger Processor – LHCC Jan 28th 2004